# **LECTURE NOTES ON**

# INTEGRATED CIRCUIT APPLICATIONS

# III B.Tech V semester Prepared by

Ms. C. Deepthi, Assistant Professor

Ms. N.Anusha, Assistant Professor

Ms. P Saritha, Assistant Professor

**ELECTRONICS AND COMMUNICATION ENGINEERING**

# INSTITUTE OF AERONAUTICAL ENGINEERING

(Autonomous)

# UNIT I INTEGRATED CIRCUITS

#### INTEGRATED CIRCUITS

An integrated circuit (IC) is a miniature, low cost electronic circuit consisting of active and passive components fabricated together on a single crystal of silicon. The active components are transistors and diodes and passive components are resistors and capacitors.

#### Advantages of integrated circuits

- 1. Miniaturization and hence increased equipment density.

- 2. Cost reduction due to batch processing.

- 3. Increased system reliability due to the elimination of soldered joints.

- 4. Improved functional performance.

- 5. Matched devices.

- 6. Increased operating speeds.

- 7. Reduction in power consumption

Depending upon the number of active devices per chip, there are different levels of integration

|   | Level of integration                | Number of active devices per chip |

|---|-------------------------------------|-----------------------------------|

| 1 | Small scale integration(SSI)        | Less then100                      |

| 2 | Medium Scale integration(MSI)       | 100-10000                         |

| 3 | Large scale integration(LSI)        | 1000-100,000                      |

| 4 | Very Large scale integration(VLSI)  | Over 100,000                      |

| 5 | Ultra Large scale integration(ULSI) | Over 1 milloin                    |

#### **IC Package Types**

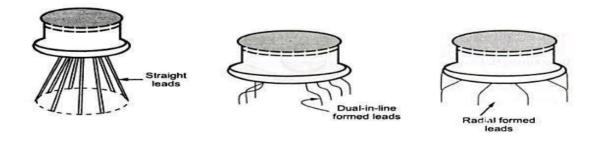

The op-amp ICs are available in various packages. The IC packages are classified as,

- 1.Metal Can

- 2.Dual In Line

- 3.Flat Pack

#### Metal Can package:

#### **Dual- in- Line Package:**

#### Flat Pack:

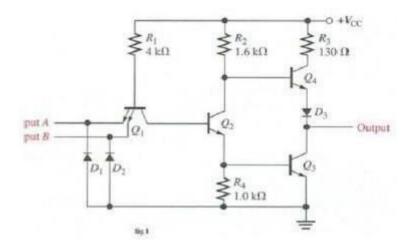

**INTERNAL CIRCUIT:**

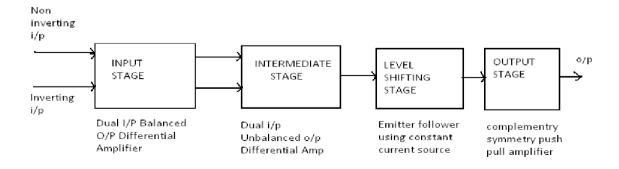

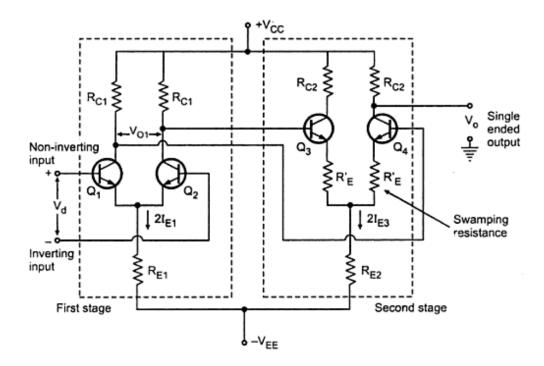

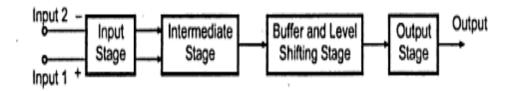

The operational amplifier is a direct-coupled high gain amplifier usable from 0 to over 1MHz to which feedback is added to control its overall response characteristic i.e. gain and bandwidth. The op-amp exhibits the gain down to zero frequency. The internal block diagram of an op-amp is shown in the fig The input stage is

the dual input balanced output differential amplifier. This stage generally provides most of the voltage gain of the amplifier and also establishes the input resistance of the op-amp. The intermediate stage is usually another differential amplifier, which is driven by the output of the first stage. On most amplifiers, the intermediate stage is dual input, unbalanced output. Because of direct coupling, the dc voltage at the output of the intermediate stage is well above ground potential. Therefore, the level translator (shifting) circuit is used after the intermediate stage downwards to zero volts with respect to ground. The final stage is usually a push pull complementary symmetry amplifier output stage. The output stage increases the voltage swing and raises the ground supplying capabilities of the op-amp. A well designed output stage also provides low output resistance.

Block Diagram of OP-AMP

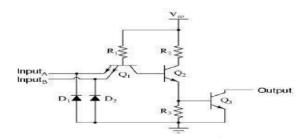

#### Differential amplifier:

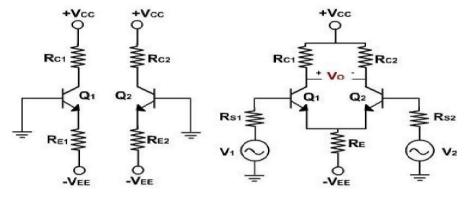

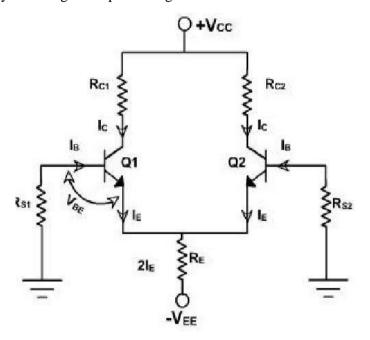

Differential amplifier is a basic building block of an op-amp. The function of a differential amplifier is to amplify the difference between two input signals. The two transistors Q1 and Q2 have identical characteristics. The resistances of the circuits are equal, i.e. RE1 = R E2, RC1 = R C2 and the magnitude of +VCC is equal to the magnitude of -VEE. These voltages are measured with respect to ground.

Differential Amplifier

To make a differential amplifier, the two circuits are connected as shown in fig. 1.4. The two +VCC and -VEE supply terminals are made common because they are same. The two emitters are also connected and the parallel combination of RE1 and RE2 is replaced by a resistance RE. The two input signals v1& v2 are applied at the base of Q1 and at the base of Q2. The output voltage is taken between two collectors. The collector resistances are equal and therefore denoted by RC = RC1 = RC2.

Ideally, the output voltage is zero when the two inputs are equal. When v1 is greater then v2 the output voltage with the polarity shown appears. When v1 is less than v2, the output voltage has the opposite polarity.

The differential amplifiers are of different configurations.

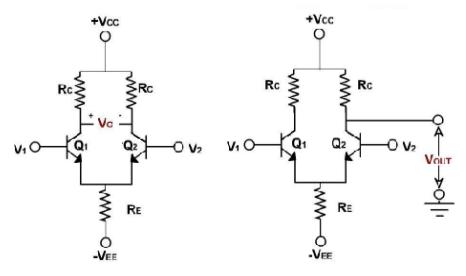

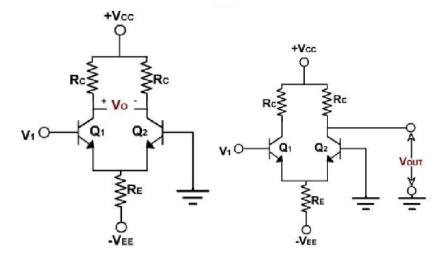

Fig. Dual input, balanced output differential amplifier. Fig. 1.6. Dual input, unbalanced output differential amplifier.

Fig..Single input, balanced output differential amplifierFig.1.8.Single input, unbalanced output differential amplifier.

The four differential amplifier configurations are following:

- 1. Dual input, balanced output differential amplifier.

- 2. Dual input, unbalanced output differential amplifier.

- 3. Single input balanced output differential amplifier.

- 4. Single input unbalanced output differential amplifier.

These configurations are shown in fig and are defined by number of input signals used and the way an output voltage is measured. If use two input signals, the configuration is said to be dual input, otherwise it is a single input configuration. On the other hand, if the output voltage is measured between two collectors, it is referred to as a balanced output because both the collectors are at the same dc potential w.r.t. ground. If the output is measured at one of the collectors w.r.t. ground, the configuration is called an unbalanced output.

A multistage amplifier with a desired gain can be obtained using direct connection between successive stages of differential amplifiers. The advantage of direct coupling is that it removes the lower cut off frequency imposed by the coupling capacitors, and they are therefore, capable of amplifying dc as well as ac input signals.

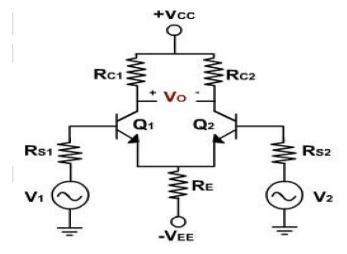

#### 1.8.1 Dual Input, Balanced Output Differential Amplifier:

The circuit is shown in figV1 and V2 are the two inputs, applied to the bases of Q1 and Q2 transistors. The output voltage is measured between the two collectors C1 and C2, which are at same dc potentials.

#### **D.C.** Analysis:

To obtain the operating point (ICQ and VCEQ) for differential amplifier dc equivalent circuit is drawn by reducing the input voltages V1 and V2 to zero as shown in fig

Fig.Differential Amplifier

The internal resistances of the input signals are denoted by RS because RS1= RS2. Since both emitter biased sections of the different amplifier are symmetrical in all respects, therefore, the operating point for only one section need to be determined. The same values of ICQ and VCEQ can be used for second transistor Q2. Applying KVL to the base emitter loop of the transistor Q1.

$$\begin{array}{l} R_{S} \mid_{B} + V_{BE} + 2 \mid_{E} R_{E} = V_{EE} \\ \\ But \mid_{B} = \frac{I_{E}}{\beta_{dc}} \; \text{and} \mid_{C} \approx \mid_{E} \\ \\ \triangle \mid_{E} = \mid_{C} = \frac{V_{EE} - V_{BE}}{2R_{E} + R_{S} / \beta_{dc}} \qquad (E-1) \\ \\ V_{BE} = 0.6 V \; \text{for} \; S_{i} \; \; \text{and} \; 0.2 V \; \text{for} \; G_{e}. \\ \\ Generally \; \frac{R_{S}}{\beta_{dc}} << 2R_{E} \; \; \text{because} \; R_{S} \; \text{is the internal resistance of input signal.} \\ \\ \triangle \mid_{E} = \mid_{C} = \frac{V_{EE} - V_{BE}}{2R_{E}} \end{array}$$

The value of RE sets up the emitter current in transistors Q1 and Q2 for a given value of VEE. The emitter current in Q1 and Q2 are independent of collector resistance RC. The voltage at the emitter of Q1 is approximately equal to -VBE if the voltage drop across R is negligible. Knowing the value of IC the voltage at the collector VCis given by

Fig Differential Amplifier

From the two equations VCEQ and ICQ can be determined. This dc analysis is applicable for all types of differential amplifier.

#### A.C. Analysis:

The circuit is shown in fig. V1 and V2 are the two inputs, applied to the bases of Q1 and Q2 transistors. The output voltage is measured between the two collectors C1 and C2, which are at same dc potentials.

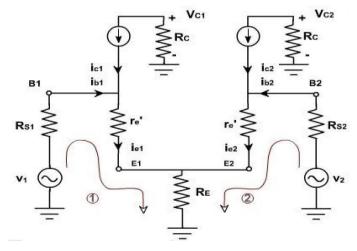

Dc analysis has been done to obtain the operating point of the two transistors. To find the voltage gain Ad and the input resistance Ri of the differential amplifier, the ac equivalent circuit is drawn using r-parameters as shown in fig. The dc voltages are reduced to zero and the ac equivalent of CE configuration is used.

Fig. Differential Amplifier A/C Analysis

Since the two dc emitter currents are equal. Therefore, resistance r'e1 and r'e2 are also equal and designated by r'e. This voltage across each collector resistance is shown 180° out of phase with respect to the input voltages v1 and v2. This is same as in CE configuration. The polarity of the output voltage is shown in Figure. The collector C2 is assumed to be more positive with respect to collector C1 even though both are negative with respect to ground.

The output voltage VO is given by

$$V_o = V_{c2} - V_{c1}$$

$$= -R_C i_{C2} - (-R_c i_{c1})$$

$$= R_C (i_{C1} - i_{c2})$$

$$= R_C (i_{s1} - i_{s2})$$

Substituting ie1, & ie2 in the above expression

$$\begin{split} V_o &= R_C \left\{ \frac{(r_s + R_E)V_1 - R_E V_2}{(r_e' + R_E)^2 - R_E^2} - \frac{(r_s + R_E)V_2 - R_E V_1}{(r_e' + R_E)^2 - R_E^2} \right\} \\ &= \frac{R_C (V_1 - V_2)(r_e' - 2R_E)}{r_e' (r_e' + 2R_E)} \\ V_o &= \frac{R_C}{r_e'} (V_1 - V_2) \dots \dots E(1) \end{split}$$

Thus a differential amplifier amplifies the difference between two input signals. Defining the difference of input signals as Vd =V1 -V2 the voltage gain of the dual input balanced output differential amplifier can be given by (E-2)

# **Differential Input Resistance:**

Differential input resistance is defined as the equivalent resistance that would be measured at either input terminal with the other terminal grounded. This means that the input resistance Ri1 seen from the input signal source V1 is determined with the signal source V2 set at zero.

$$R_{i1} = \frac{v_1}{i_{b1}} \Big|_{V_2} = 0$$

$$= \frac{v_1}{i_{a1}/\beta} \Big|_{V_2} = 0$$

$$R_{i1} = \frac{\beta r'_{e}(r'_{e} + 2R_{E})}{r'_{e} + R_{E}}$$

Since  $R_{E} >> r'_{e}$

$$\therefore r'_{e} + 2R_{E} >> 2R_{E}$$

Similarly, the input signal V1 set at zero to determine the input resistance Ri2 seen from the input signal source V2. Resistance RS1 and RS2 are ignored because they are very small.

Subtuting ie 1,

Similarly

$$R_{i2} = \frac{V_2}{i_{b2}} \Big|_{V_1 = 0}$$

$$= \frac{V_2}{i_{e2} / \beta} \Big|_{V_1 = 0}$$

$$R_{i2} = 2\beta r'_e \quad (E-4)$$

The factor of 2 arises because the re' of each transistor is in series. To get very high input impedance with differential amplifier is to use Darlington transistors. Another ways is to use FET.

# **Output Resistance:**

Output resistance is defined as the equivalent resistance that would be measured at output terminal with respect to ground. Therefore, the output resistance RO1 measured between collector C1 and ground is equal to that of the collector resistance RC. Similarly the output resistance RO2 measured at C2 with respect to ground is equal to that of the collector resistor RC.

$$RO1 = RO2 = RC (E-5)$$

The current gain of the differential amplifier is undefined. Like CE amplifier the differential amplifier is a small signal amplifier. It is generally used as a voltage amplifier and not as current or power amplifier.

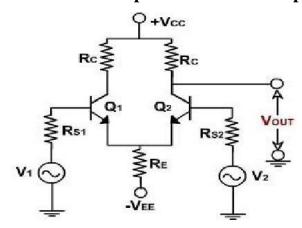

#### **Dual Input, Unbalanced Output Differential Amplifier:**

#### Differential Amplifier

In this case, two input signals are given however the output is measured at only one of the two- collector w.r.t. ground as shown infig1.12. The output is referred to as an unbalanced output because the collector at which the output voltage is measured is at some finite dc potential with respect to ground.

In other words, there is some dc voltage at the output terminal without any input signal applied. DC analysis is exactly same as that of first case.

$$I_{E} = I_{CQ} = \frac{V_{EE} - V_{BE}}{2R_{E} + R_{2} / \beta_{dc}}$$

$$V_{CEQ} = V_{CC} + V_{BE} - I_{CQ}R_{C}$$

AC Analysis:

The output voltage gain in this case is given by

$$A_{d} = \frac{V_{0}}{V_{d}} = \frac{R_{C}}{2r'_{e}}$$

The voltage gain is half the gain of the dual input, balanced output differential amplifier. Since at the output there is a dc error voltage, therefore, to reduce the voltage to zero, this configuration is normally followed by a level translator circuit.

#### **DIFFERENTIAL AMPLIFIER:**

The differential amplifier consists of two symmetrical common-emitter sections and is capable of amplifying the difference between two input signals. The differential amplifier can amplify ac as well as dc input signals because it employs direct coupling.

There are four types of differential amplifier configurations:

(a) The dual Input, Balanced output differential

amplifier DC Analysis

$$I_{\text{E}}$$

=  $V_{\text{EE}}$  -  $V_{\text{BE}}$ /2 $R_{\text{E}}$ ,

$$V_{\text{CE}}$$

= $V_{\text{CC}}$ +  $V_{\text{BE}}$ - $R_{\text{c}}I_{\text{c}}$  AC Analysis -------  $A_d$ = $R_{\text{C}}/r_e$

$$R_{i1}$$

= $R_{i2}$ =2 $\beta_{ac}r_e$

$$R_{01}$$

= $R_{02}$ = $R_c$

(b) The dual input, unbalanced output differential

Amplifier DC Analysis I\_E =V\_{EE} - V\_{BE}/(2R\_E + R\_{in}/\beta\_{dc})

$$V_{CE} = V_{CC} + V_{BE} - R_c I_{CQ}$$

$$AC \ Analysis ------ A_d = R_C/2r_e$$

$$R_{i1} =$$

$$R_{i2} = 2\beta_{ac}r_e$$

$R_0 = R_c$

Amplifier DC Analysis  $I_E = V_{EE} - V_{BE}/(2R_E + R_{in}/\beta_{dc})$

(c) The single input, balanced output differential

$$V_{CE} = V_{CC} + V_{BE} - R_c I_{CQ}$$

AC Analysis -----

$$I_E = V_{EE} - V_{BE} / (2R_E + R_{in}/\beta_{dc})$$

$$R_i = 2\beta$$

$$a_c r_e$$

$$R_{01} = R_0$$

$$_2 = R_c$$

(d) The single input, unbalanced output differential

Amplifier DC Analysis I

$$_{E}$$

=V  $_{EE}$  - V  $_{BE}$  /(2R  $_{E}$  +R  $_{in}$  / $\beta_{dc}$ )

$$V_{CE}$$

=V  $_{CC}$  + V  $_{BE}$  -R  $_{c}$  I  $_{CQ}$

$$AC\ Analysis ----- A_d\!\!=\!\!R_C\!/2r_e$$

$R_{i\text{=}}2\beta_{ac}r_{e}$

$R_0 = R_c$

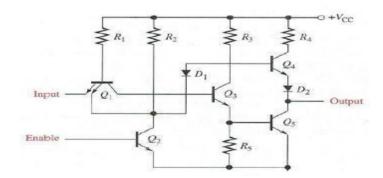

# **Cascade Differential Amplifier Stages:**

In cascaded differential amplifier, the output of the first stage is used as an input for the second stage, the output of the second stage is applied as an input to the third stage, and so on. Because of direct coupling between the stages, the operating point of succeeding stages changes

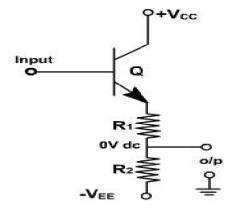

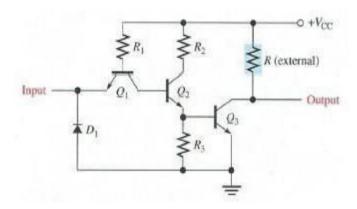

#### **Level Translator:**

Because of the direct coupling the dc level at the emitter rises from stages to stage. This increase in dc level tends to shift the operating point of the succeeding stages and therefore limits the output voltage swing and may even distort the output signal.

To shift the output dc level to zero, level translator circuits are used. An emitter follower with voltage divider is the simplest form of level translator as shown in fig Thus a dc voltage at the base of Q produces 0V dc at the output. It is decided by R1 and R2. Instead of voltage divider emitter follower either with diode current bias or current mirror bias as shown in fig may be used to get better results.

Fig Common collector Amplifier

In this case, level shifter, which is common collector amplifier, shifts the level by 0.7V. If this shift is not sufficient, the output may be taken at the junction of two resistors in the emitter leg.

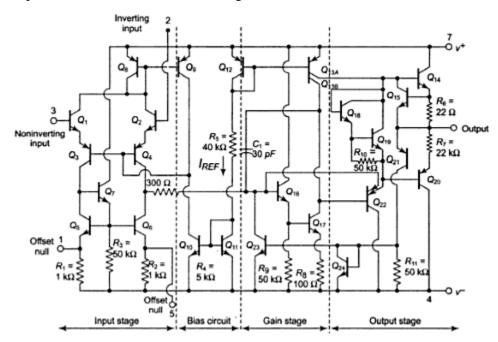

Fig shows a complete op-amp circuit having input different amplifiers with balanced output, intermediate stage with unbalanced output, level shifter and an output amplifier.

#### characteristics Op-amp

#### **DC** characteristics:

#### a) Input offset voltage:

Input offset voltage Vio is the differential input voltage that exists between two input terminals of an op-amp without any external inputs applied. In other words, it is the amount of the input voltage that should be applied between two input terminals in order to force the output voltage to zero. Let us denote the output offset voltage due to input offset voltage Vio as Voo. The output offset voltage Voo is caused by mismatching between two input terminals. Even though all the components are integrated on the same chip, it is not possible to have two transistors in the input differential amplifier stage with exactly the same characteristics. This means that the collector currents in these two transistors are not equal, which causes a differential output voltage from the first stage. The output of first stage is amplified by following stages and possibly aggravated by more mismatching in them.

Fig Input offset voltage in op-amp

Fig Output offset voltage in op-amp

Fig .Op-Amp with offset voltage compensating network

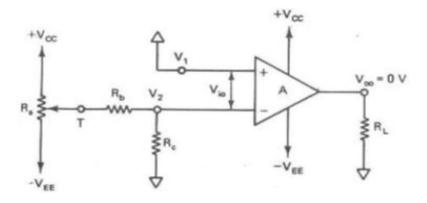

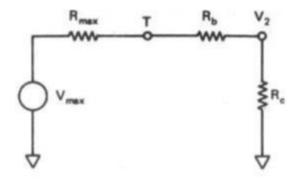

The op-amp with offset-voltage compensating network is shown in Figure The Compensating network consists of potentiometer Ra and resistors Rb and Re. To establish a relationship between Vio, supply voltages, and the compensating components, first Thevenize the circuit, looking back into Ra from point T. The maximum Thevenin's equivalent resistance Rmax, occurs when the wiper is at the center of the Potentiometer, as shown in Figure.

$$Rmax = (R a / 2) || (R a / 2)$$

Supply voltages VCC and -VEE are equal in magnitude therefore; let us denote their magnitude by voltage V.

Thus  $V \max = V$ .

where V2 has been expressed as a function of maximum Thevenin's voltage Vmax and maximum Thevenin's resistance, But the maximum value of V2 can be equal to Vio since V1— V2 = Vio. Thus Equation becomes

$$V_2 = \frac{R_c}{R_{\text{max}} + R_b + R_c} V_{\text{max}}$$

$$V_{io} = \frac{R_c}{R_{\text{max}} + R_b + R_c} V_{\text{max}}$$

Assume Rb >Rmax >Rc, where Rmax = Ra/4. Using this assumption Rmax+Rb+Rc=Rb Therefore

$$V_{io} = rac{R_c V_{ ext{max}}}{R_b}$$

$V_{ ext{max}} = V = |V_{CC}| = |-V_{EE}|$   $V_{io} = rac{R_c V}{R_b}$

where

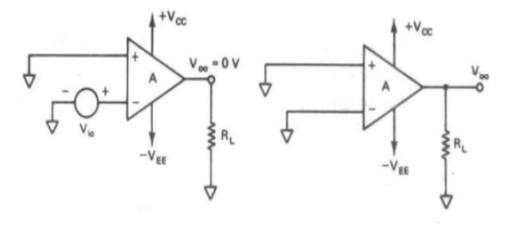

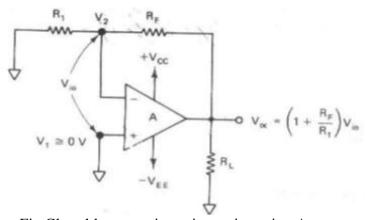

Let us now examine the effect of *Vio* in amplifiers with feedback. The non-inverting and inverting amplifiers with feedback are shown in Figure. To determine the effect of Vio, in each case, we have to reduce the input voltage vin to zero.

Fig Closed loop non inverting or inverting Amp

With vin reduced to zero, the circuits of both non-inverting and inverting amplifiers are the sameas the circuit in Figure. The internal resistance Rin of the input signal voltage is negligibly small. In the figure, the non-inverting input terminal is connected to ground; therefore, assume voltage V1 at input terminal to be zero. The voltageV2 at the inverting input terminal can be determined by applying the voltage-divider rule:

$$V_2 = \frac{R_1 V_{oo}}{R_1 + R_F}$$

Therefore,

$$V_{oo} = \frac{R_1 + R_F}{R_1} V_2$$

Since  $V_{io} = |V_1 - V_2|$  and  $V_1 = 0$  V,  $V_{io} = |0 - V_2| = V_2$

$$V_{io} = |0 - V_2| = V_2$$

Therefore,

$$V_{oo} = \left(1 + \frac{R_F}{R_1}\right) V_{io} = (A_{oo}) V_{io}$$

#### a) Input offset voltage

A small voltage applied to the input terminals to make the output voltage as zero when the two input terminals are grounded is called input offset voltage

#### b) Input bias current

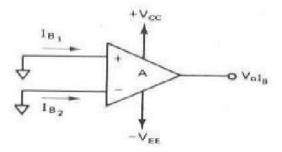

Input bias current IB as the average value of the base currents entering into terminal of an op- amp.

#### c) Input bias current

Input bias current IB as the average value of the base currents entering into terminal of an op- amp.

$$I_B = \frac{I_{B1} + I_{B2}}{2}$$

where  $I_{B1}$  = dc bias current flowing into the noninverting input  $I_{B2}$  = dc bias current flowing into the inverting input

I<sub>B</sub>=|<sub>B1</sub>=|<sub>B2</sub>

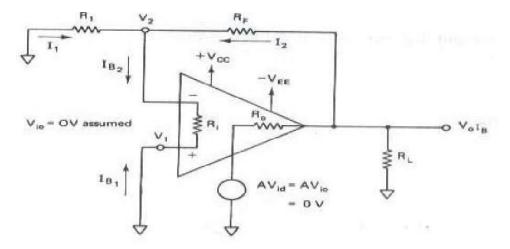

Obtaining the expression for the output offset voltage caused by the input bias current IB in the inverting and non-inverting amplifiers and then devise some scheme to eliminate or minimize it.

In the figure, the input bias currents '81 and I are flowing into the non-inverting and inverting input leads, respectively. The non-inverting terminal is connected to ground; therefore, the voltage VI = 0 V. The controlled voltage source A Vio = 0 V since Vio = 0 V is assumed. With output resistance Ro is negligibly small, the right end of RF is essentially at ground potential; that is, resistors RI, and RF are in parallel and the bias current I, flows through them. Therefore, the voltage at the inverting terminal is

#### d) Thermal Drift:

Bias current, offset current and offset voltage change with temperature. A circuit carefully nulled at 25oc may not remain so when the temperature rises to 35oc. This is called thermal drift.

#### **AC CHARACTERISTICS:**

#### a) Slew Rate

The slew rate is defined as the maximum rate of change of output voltage caused by a step input voltage. An ideal slew rate is infinite which means that opamp's output voltage should change instantaneously in response to input step voltage.

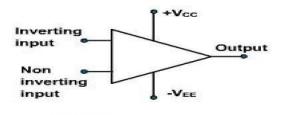

The symbolic diagram of an OPAMP is shown in fig

Fig. Op-Amp Symbol

#### b) Frequency Response

Need for frequency compensation in practical op-amps:

Frequency compensation is needed when large bandwidth and lower closed loop gain is desired. Compensating networks are used to control the phase shift and hence to improve the stability

Frequency compensation methods: a) Dominant- pole compensation b) Pole- zero compensation.

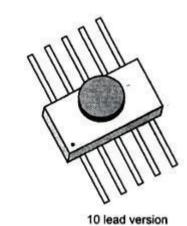

741c is most commonly used OPAMP available in IC package. It is an 8-pin DIP chip.

#### Block diagram of op-amp:

The block diagram of IC op-amp is as shown in figure

#### **Ideal OP-AMP**

An ideal OP-AMP would have the following characteristics:

- 1. The input resistance  $R_{\rm IN}$  would be infinite

- 2. The output resistance  $R_{OUT}$  would be zero

- 3. The voltage gain, V<sub>G</sub> would be infinite

- 4. The bandwidth (how quickly the output will follow the input) would be infinite

- 5. If the voltages on the two inputs are equal than the output voltage is zero ( If the output is not zero it is said to have an offset)

#### **Op-amp 741:**

The IC 741 is high performance monolithic op-amp IC .It is available in 8 pin, 10 pin or 14 pin configuration. It can operate over a temperature of -55 to 125 centigrade.op-amp 741 equivalent circuit is as shown in figure.

#### Features of IC-741

- No frequency compensation required.

- Short circuit protection provided.

- Offset voltage null capability.

- Large common mode and Differential voltage range.

- No latch up.

- No External frequency compensation is required

- Short circuit Protection

- Low Power Dissipation

#### **Parameters of OPAMP:**

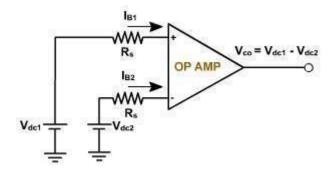

#### 1. Input Offset Voltage:

Fig. Input offset voltage

If no external input signal is applied to the op-amp at the inverting and non-inverting terminals the output must be zero. That is, if Vi=0, Vo=0. But as a result of the given biasing supply voltages, +Vcc and -Vcc, a finite bias current is drawn by the op-amps, and as a result of asymmetry on the differential amplifier configuration, the output will not be zero. This is known as offset. Since Vo must be zero when Vi=0 an input voltage must be applied such that the output offset is cancelled and Vo is made zero. This is known as input offset voltage. Input offset voltage (Vio) is defined as the voltage that must be applied between the two input terminals of an OPAMP to null or zero the output voltage. Fig 1.22 shows that two dc voltages are applied to input terminals to make the output zero.

$$Vio = Vdc1 - Vdc2$$

Vdc1 and Vdc2 are dc voltages and RS represents the source resistance. Vio is the difference of Vdc1 and Vdc2. It may be positive or negative. For a 741C OPAMP the maximum value of Vio is 6mV. It means a voltage  $\pm 6 mV$  is required to one of the input to reduce the output offset voltage to zero. The smaller the input offset voltage the better the differential amplifier, because its transistors are more closely matched.

#### **Input offset Current:**

Though for an ideal op-amp the input impedance is infinite, it is not so practically. So the IC draws current from the source, however smaller it may be. This is called input offset current Iio. The input offset current Iio is the difference between the currents into inverting and non-inverting terminals of a balanced amplifier as shown in fig

The Iio for the 741C is 200nA maximum. As the matching between two input terminals is improved, the difference between IB1 and IB2 becomes smaller, i.e. the Iio value decreases further. For a precision OPAMP 741C, Iio is 6 nA

#### **Input Bias Current:**

The input bias current IB is the average of the current entering the input terminals of a balanced amplifier i.e.

$$IB = (IB1 + IB2) / 2$$

For ideal op-amp IB=0. For 741C IB(max) = 700 nA and for precision 741C IB =  $\pm$  7 nA

# **Differential Input Resistance: (Ri)**

Ri is the equivalent resistance that can be measured at either the inverting or non- inverting input terminal with the other terminal grounded. For the 741C the input resistance is relatively high 2 M $\Omega$ . For some OPAMP it may be up to 1000 G ohm.

#### **Input Capacitance: (Ci)**

Ci is the equivalent capacitance that can be measured at either the inverting and non inverting terminal with the other terminal connected to ground. A typical value of Ci is 1.4 pf for the 741C.

#### **Offset Voltage Adjustment Range:**

741 OPAMP have offset voltage null capability. Pins 1 and 5 are marked offset null for this purpose. It can be done by connecting 10 K ohm pot between 1 and 5.

By varying the potentiometer, output offset voltage (with inputs grounded) can be reduced to zero volts. Thus the offset voltage adjustment range is the range through which the input offset voltage can be adjusted by varying 10 K pot. For the 741C the offset voltage adjustment range is  $\pm$  15 mV.

#### **Input Voltage Range:**

Input voltage range is the range of a common mode input signal for which a differential amplifier remains linear. It is used to determine the degree of matching between the inverting and non-inverting input terminals. For the 741C, the range of the input common mode voltage is  $\pm$  13V maximum. This means that the common mode voltage applied at both input terminals can be as high as +13V or as low as -13V.

# **Large Signal Voltage Gain:**

Since the OPAMP amplifies difference voltage between two input terminals, the voltage gain of the amplifier is defined as

Voltage gain =

$$\frac{\text{Output voltage}}{\text{Differential input voltage}}$$

$$A = \frac{V_0}{V_{id}}$$

Because output signal amplitude is much large than the input signal the

voltage gain is commonly called large signal voltage gain. For 741C is voltage gain is 200,000 typically.

#### **Output voltage Swing:**

The ac output compliance PP is the maximum unclipped peak to peak output voltage that an OPAMP can produce. Since the quiescent output is ideally zero, the ac output voltage can swing positive or negative. This also indicates the values of positive and negative

saturation voltages of the OP-AMP. The output voltage never exceeds these limits for a given supply voltages +VCC and -VEE. For a 741C it is  $\pm$  13 V.

#### **Output Resistance: (RO)**

RO is the equivalent resistance that can be measured between the output terminal of the OPAMP and the ground. It is 75 ohm for the 741C OPAMP.

#### **Output Short circuit Current:**

In some applications, an OPAMP may drive a load resistance that is approximately zero. Even its output impedance is 75 ohm but cannot supply large currents. Since OPAMP is low power device and so its output current is limited. The 741C can supply a maximum short circuit output current of only 25mA.

#### **Supply Current:**

IS is the current drawn by the OP-AMP from the supply. For the 741C OPAMP the supply current is 2.8 m A.

# **Power Consumption:**

Power consumption (PC) is the amount of quiescent power (Vin= 0V) that must be consumed by the OPAMP in order to operate properly. The amount of power consumed by the 741C is 85 mW.

#### **Gain Bandwidth Product:**

The gain bandwidth product is the bandwidth of the OPAMP when the open loop voltage gain is reduced to

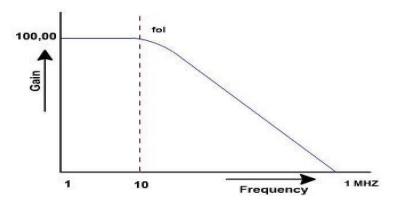

1.32.1 From open loop gain vs frequency graph At 1 MHz shown in.fig.1.24,it can be found 1 MHz for the 741C OPAMP frequency the gain reduces to 1. The mid band voltage gain is 100, 000 and

cut off frequency is 10Hz.

Fig.1.24 Band width of OP-AMP

#### **Slew Rate:**

The maximum rate of change of output voltage with respect to time is called Slew rate of the Op-amp.

It is expressed as,  $S = \max_{max}$  and measured in

V/sec. The Slew rate equation is,  $S = 2\pi f V_m$

V/sec

# Common Mode Rejection Ratio (CMRR).

CMRR is defined as the ratio of the differential voltage gain Ad to the common mode voltage gain

$$ACM CMRR = Ad / ACM.$$

For the 741C, CMRR is 90 dB typically. The higher the value of CMRR the better is the matching between two input terminals and the smaller is the output common mode voltage.

#### PSRR:

PSRR is Power Supply Rejection Ratio. It is defined as the change in the input offset voltage due to the change in one of the two supply voltages when other voltage is

maintained constant. It's ideal value should be Zero.

**Slew Rate:** Slew rate is defined as the maximum rate of change of output voltage per unit of time under large signal conditions and is expressed in volts / μsecs.

To understand this, consider a charging current of a capacitor

$$i = C \frac{dV}{dt}$$

$$\frac{dV}{dt} = \frac{i}{\sqrt{c}}$$

If 'i' is more, capacitor charges quickly. If 'i' is limited to Imax, then rate of change is also limited. Slew rate indicates how rapidly the output of an OP-AMP can change in response to changes in the input frequency with input amplitude constant. The slew rate changes with change in voltage gain and is normally specified at unity gain.

If the slope requirement is greater than the slew rate, then distortion occurs. For the 741C the slew rate is low  $0.5~V~/\mu S$  which limits its use in higher frequency applications.

#### **Input Offset Voltage and Current Drift:**

It is also called average temperature coefficient of input offset voltage or input offset current. The input offset voltage drift is the ratio of the change in input offset voltage to change in temperature and expressed in  $\Delta V$  /° C. Input offset voltage drift = ( $\Delta V$ io / $\Delta T$ ). Similarly, input offset current drift is the ratio of the change in input offset current to the change in temperature. Input offset current drift = ( $\Delta I$ io / $\Delta T$ ).

For 741C,

$$\Delta Vio / \Delta T = 0.5 V / C. \Delta Iio / \Delta T = 12 pA / C$$

# Unit 2

# **Op-amp Applications**

# SUMMING, SCALING, AND AVERAGING AMPLIFIERS Inverting Configuration

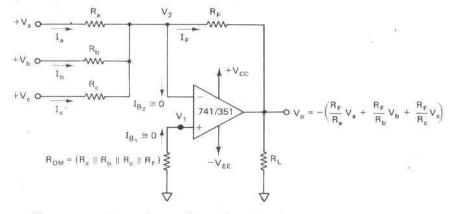

Figure shows the inverting configuration with three inputs Va, Vb, and Vc. Depending on the relationship between the feedback resistor  $R_f$  and the input resistors Ra, Rb, and Rc, the circuit can be used as either a summing amplifier, scaling amplifier, or averaging amplifier. The circuit's function can be verified by examining the expression for the output voltage V0, which is obtained from Kirchhoff's current equation written at node V2. Referring to Figure

**Figure** Inverting configuration with three inputs can be used as a summing amplifier, scaling amplifier, or averaging amplifier.

$$I_a + I_b + I_c = I_B + I_F$$

Since  $R_i$  and A of the op-amp are ideally infinity,  $I_B = 0$  A and  $V_1 = V_2 \cong 0$  V. Therefore,

$$\frac{V_a}{R_a} + \frac{V_b}{R_b} + \frac{V_c}{R_c} = -\frac{V_a}{R_F}$$

or ·

$$V_o = -\left(\frac{R_F}{R_a} V_a + \frac{R_F}{R_b} V_b + \frac{R_F}{R_c} V_c\right)$$

# Summing amplifier.

$$V_o = -\frac{R_F}{R} \left( V_a + V_b + V_c \right)$$

#### If Ra=Rb=Rc=R then

This means that the output voltage is equal to the *negative* sum of all the inputs times the gain of the circuit  $R_F/R$ ; hence the circuit is called a *summing amplifier*. Obviously, when the gain of the circuit is 1, that is,  $R_a = R_b = R_c = R_F$ , the output voltage is equal to the *negative* sum of all input voltages. Thus

$$V_o = -(V_a + V_b + V_c)$$

**Scaling or weighted amplifier.** If each input voltage is amplified by a different factor, in other words, weighted differently at the output, the circuit in Figure is then called a *scaling* or *weighted amplifier*. This condition can be accomplished if  $R_a$ ,  $R_b$ , and  $R_c$  are different in value. Thus the output voltage of the scaling amplifier is

$$V_o = -\left(\frac{R_F}{R_a} V_a + \frac{R_F}{R_b} V_b + \frac{R_F}{R_c} V_c\right)$$

where

$$\frac{R_F}{R_a} \neq \frac{R_F}{R_b} \neq \frac{R_F}{R_c}$$

# Average circuit.

The circuit of Figure can be used as an averaging circuit, in which the output voltage is equal to the average of all the input voltages. This is accomplished by using all input resistors of equal value,  $R_a = R_b = R_c = R$ . In addition, the gain by which each input is amplified must be equal to 1 over the number of inputs; that is,

$$\frac{R_F}{R} = \frac{1}{n}$$

where n is the number of inputs.

# Noninverting Configuration

Again, to verify the functions of the circuit, the expression for the output voltage must be obtained. Recall that the input resistance  $R_{iF}$  of the noninverting amplifier is very large (see Figure . Therefore, using the superposition theorem, the voltage  $V_1$  at the noninverting terminal is

$$V_1 = \frac{R/2}{R + R/2} V_a + \frac{R/2}{R + R/2} V_b + \frac{R/2}{R + R/2} V_c$$

OT

$$V_{1} = \frac{V_{a}}{3} + \frac{V_{b}}{3} + \frac{V_{c}}{3} = \frac{V_{a} + V_{b} + V_{c}}{3}$$

$$\downarrow V_{1} + V_{cc}$$

$$\downarrow V_{1} + V_{cc}$$

$$\downarrow V_{1} + V_{2} + V_{3} + V_{4} + V_{5} + V_{5} + V_{5} + V_{6} + V_{6$$

Hence the output voltage  $V_o$  is

$$V_o = \left(1 + \frac{R_F}{R_1}\right) V_1$$

$$= \left(1 + \frac{R_F}{R_1}\right) \frac{V_a + V_b + V_c}{3}$$

Averaging amplifier. If  $(1+R_F/R_1)=1$ ; It will be averaging amplifier.

Summing amplifier. If  $(1+R_F/R_1)=3$ ; It will be summing amplifier. Scaling or weighted amplifier. It is basically scaling amplifier.

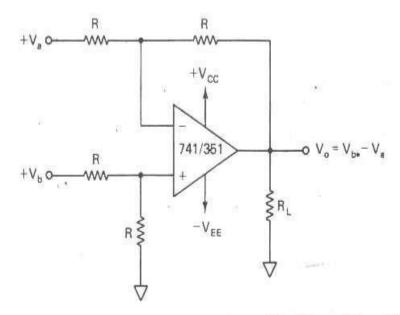

# Differential Configuration

#### A subtractor.

From this figure, the output voltage of the differential amplifier with a gain of 1 is

$$V_o \doteq -\frac{R}{R} \left( V_a - V_b \right)$$

That is,

$$V_o = V_b - V_a$$

# INSTRUMENTATION AMPLIFIER

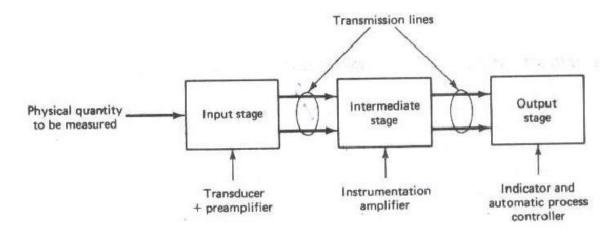

In many industrial and consumer applications the measurement and control of physical conditions are very important. For example, measurements of temperature and humidity inside a dairy or meat plant permit the operator to make necessary adjustments to maintain product quality. Similarly, precise temperature control of a plastic furnace is needed to produce a particular type of plastic.

Generally, a transducer is used at the measuring site to obtain the required information easily and safely. The *transducer* is a device that converts one form of energy into another.

Figure 7-11 Block diagram of an instrumentation system.

An instrumentation system is used to measure the output signal produced by a transducer and often to control the physical signal producing it.

The input stage is composed of a preamplifier and some sort of transducer, depending on the physical quantity to be measured. The output stage may use devices such as meters, oscilloscopes, charts, or magnetic recoders.

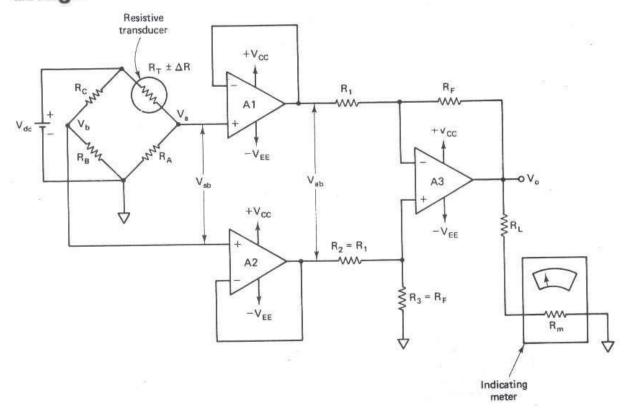

# Instrumentation Amplifier Using Transducer Bridge

A resistive transducer whose resistance changes as a function of some physical energy is connected in one arm of the bridge with a small circle around it and is denoted by  $(R_T \pm \Delta R)$ , where  $R_T$  is the resistance of the transducer and  $\Delta R$  the change in resistance  $R_T$ .

The bridge in the circuit of Figure is dc excited but could be ac excited

as well. For the balanced bridge at some reference condition,

$$V_b = V_a$$

or

$$\frac{R_B(V_{dc})}{R_B + R_C} = \frac{R_A(V_{dc})}{R_A + R_T}$$

That is,

$$\frac{R_C}{R_B} = \frac{R_T}{R_A}$$

The bridge is balanced initially at a desired reference condition. However, as the physical quantity to be measured changes, the resistance of the transducer also changes, which causes the bridge to unbalance  $(V_a \neq V_b)$ . The output voltage of the bridge can be expressed as a function of the change in resistance of the transducer, as described next.

Let the change in resistance of the transducer be  $\Delta R$ . Since  $R_B$  and  $R_C$  are fixed resistors, the voltage  $V_b$  is constant. However, voltage  $V_a$  varies as a function of the change in transducer resistance. Therefore, according to the voltage-divider rule,

$$V_a = \frac{R_A(V_{\rm dc})}{R_A + (R_T + \Delta R)}$$

$$V_b = \frac{R_B(V_{\rm dc})}{R_B + R_C}$$

Consequently, the voltage  $V_{ab}$  across the output terminals of the bridge is

$$V_{ab} = V_a - V_b$$

$$= \frac{R_A V_{dc}}{R_A + R_T + \Delta R} - \frac{R_B V_{dc}}{R_B + R_C}$$

However, if  $R_A = R_B = R_C = R_T = R$ , then

$$V_{ab} = -\frac{\Delta R(V_{dc})}{2(2R + \Delta R)}$$

The negative (-) sign in this equation indicates that  $V_a < V_b$  because of the increase in the value of  $R_T$ .

The output voltage  $V_{ab}$  of the bridge is then applied to the differential instrumentation amplifier composed of three op-amps (see Figure ). The voltage followers preceding the basic differential amplifier help to eliminate loading of the bridge circuit. The gain of the basic differential amplifier is  $(-R_F/R_1)$ ; therefore, the output  $V_o$  of the circuit is

$$V_o = V_{ab} \left( -\frac{\kappa_F}{R_1} \right) = \frac{(\Delta R)V_{dc}}{2(2R + \Delta R)} \frac{R_F}{R_1}$$

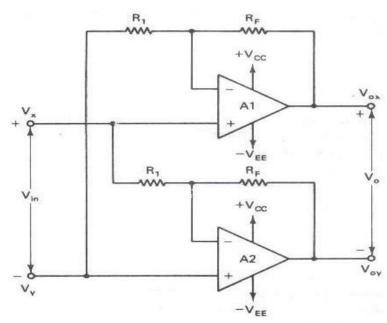

# DIFFERENTIAL INPUT AND DIFFERENTIAL OUTPUT AMPLIFIER

superposition theorem, the output  $V_{ox}$  due to inputs  $V_x$  and  $V_y$  is

$$V_{ox} = \left(1 + \frac{R_F}{R_1}\right) V_x - \left(\frac{R_F}{R_1}\right) V_y$$

Similarly, the output  $V_{oy}$  is

$$V_{oy} = \left(1 + \frac{R_F}{R_1}\right) V_y - \left(\frac{R_F}{R_1}\right) V_x$$

However, the differential output  $V_o$  is

$$V_o = V_{ox} - V_{oy}$$

Therefore, from Equations (7-18a) and (7-18b),

$$V_o = \left(1 + \frac{R_F}{R_1}\right) V_x - \left(\frac{R_F}{R_1}\right) V_y - \left(1 + \frac{R_F}{R_1}\right) V_y + \left(\frac{R_F}{R_1}\right) V_x$$

$$= \left(1 + \frac{2R_F}{R_1}\right) (V_x - V_y)$$

or

$$V_o = \left(1 + \frac{2R_F}{R_1}\right) V_{\rm in}$$

This means that the differential input and output are in phase or of the same polarity provided that  $V_{in} = V_x - V_y$  and  $V_o = V_{ox} - V_{oy}$ .

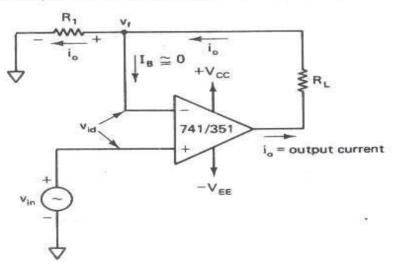

# VOLTAGE-TO-CURRENT CONVERTER WITH FLOATING LOAD

Figure shows a voltage-to-current converter in which load resistor  $R_L$  is floating (not connected to ground). The input voltage is applied to the noninverting input terminal, and the feedback voltage across  $R_1$  drives the inverting input terminal. This circuit is also called a current-series negative feedback amplifier because the feedback voltage across  $R_1$  (applied to the inverting terminal) depends on the output current  $i_o$  and is in series with the input difference voltage  $v_{id}$ .

Writing Kirchhoff's voltage equation for the input loop,

$$v_{\rm in} = v_{id} + v_f$$

But  $v_{id} \approx 0$  V, since A is very large; therefore,

$$v_{\rm in} = v_{\rm f}$$

$$v_{\rm in} = R_1 i_o$$

or

$$i_o = rac{v_{

m in}}{R_1}$$

The voltage-to-current converter can be used in such applications as low-voltage dc and ac voltmeters, diode match finders, light-emitting diodes (LEDs), and zener diode testers.

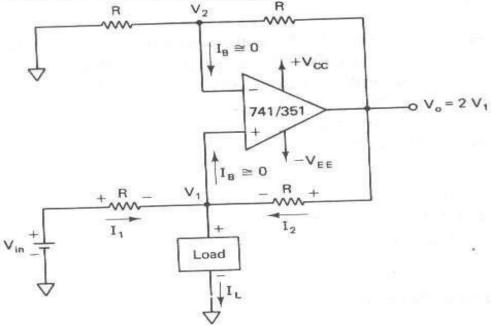

# VOLTAGE-TO-CURRENT CONVERTER WITH GROUNDED LOAD

The analysis of the circuit is accomplished by first determining the voltage  $V_1$  at the noninverting input terminal and then establishing the relationship between  $V_1$  and the load current.

Writing Kirchhoff's current equation at node  $V_1$ ,

$$I_1 + I_2 = I_L$$

$rac{V_{

m in} - V_1}{R} + rac{V_o - V_1}{R} = I_L$   $V_{

m in} + V_o - 2V_1 = I_L R$

Therefore,

$$V_1 = \frac{V_{\rm in} + V_o - I_L R}{2}$$

Since the op-amp is connected in the noninverting mode, the gain of the circuit in Figure is 1 + R/R = 2. Then the output voltage is

$$V_o = 2V_1$$

$$= V_{\rm in} + V_o - I_L R$$

That is,

$$V_{\rm in} = I_L R$$

or

$$I_L = \frac{V_{\text{in}}}{R}$$

This means that the load current depends on the input voltage  $V_{in}$  and resistor R. Notice that all resistors must be equal in value.

The voltage-to-current converter of Figure 7-19 may also be used in testing such devices as zeners and LEDs forming a ground load. However, the circuit will perform satisfactorily provided that load size  $\leq R$  value.

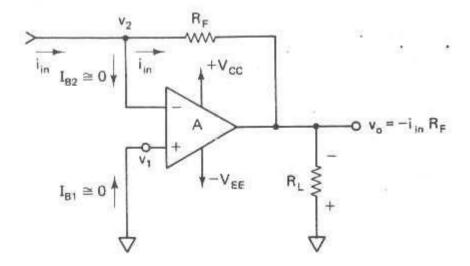

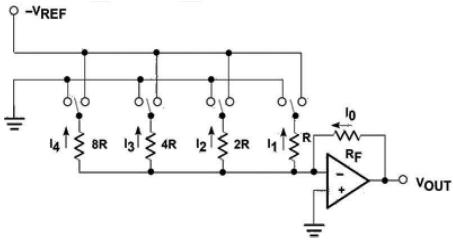

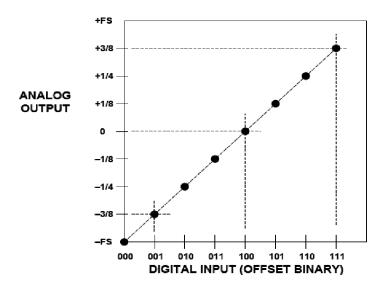

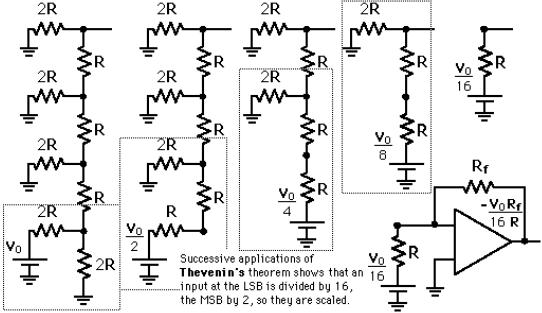

# CURRENT-TO-VOLTAGE CONVERTER

the current-to-voltage (I-to-V) converter was presented as a special case of the inverting amplifier in which an input current is converted into a proportional output voltage. One of the most common uses of the current-to-voltage converter is in digital-to-analog circuits (DACs) and in sensing current through photodetectors such as photocells, photodiodes, and photovoltaic cells. Photosensitive devices produce a current that is proportional to an incident radiant energy or light and therefore can be used to detect the light.

Let us reconsider the ideal voltage-gain Equation

of the inverting amplifier,

$$\frac{v_o}{v_{\rm in}} = -\frac{R_F}{R_1}$$

Therefore,

$$v_o = -\left(\frac{v_{\rm in}}{R_1}\right) R_F$$

However, since  $v_1 = 0$  V and  $v_1 = v_2$ .

$$\frac{v_{\rm in}}{R_1}=i_{\rm in}$$

and

$$v_o = -i_{in}R_F$$

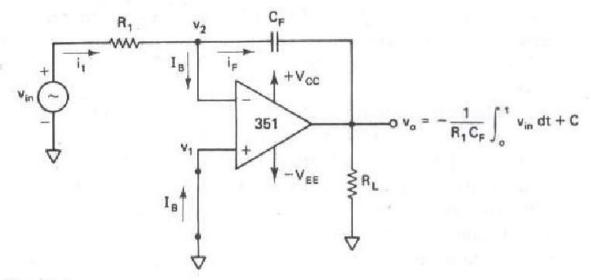

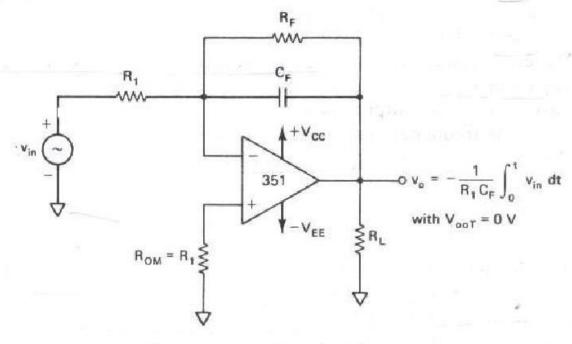

# THE INTEGRATOR

A circuit in which the output voltage waveform is the integral of the input voltage waveform is the *integrator* or the *integration amplifier*. Such a circuit is obtained by using a basic inverting amplifier configuration if the feedback resistor  $R_F$  is replaced by a capacitor  $C_F$

The expression for the output voltage  $v_o$  can be obtained by writing Kirchhoff's current equation at node  $v_2$ :

$$i_1 = I_B + i_F$$

Since  $I_B$  is negligibly small,

$$i_1 \cong i_F$$

Recall that the relationship between current through and voltage across the capacitor is

$$i_c = C \frac{dv_c}{dt}$$

Therefore.

$$\frac{v_{\rm in}-v_2}{R_1}=C_F\left(\frac{d}{dt}\right)(v_2-v_o)$$

However,  $v_1 = v_2 \approx 0$  because A is very large. Therefore,

$$\frac{v_{\rm in}}{R_1} = C_F \frac{d}{dt} \left( -v_o \right)$$

The output voltage can be obtained by integrating both sides with respect to time:

$$\int_0^t \frac{v_{\text{in}}}{R_1} dt = \int_0^t C_F \frac{d}{dt} (-v_o) dt$$

$$= C_F(-v_o) + v_o|_{t=0}$$

Therefore,

$$v_o = -\frac{1}{R_1 C_F} \int_0^t v_{\rm in} \ dt + C$$

where C is the integration constant and is proportional to the value of the output voltage  $v_o$  at time t = 0 seconds.

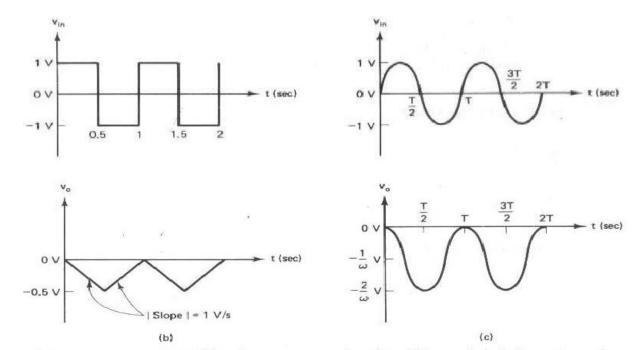

**Figure** (a) The integrator circuit. (b) and (c) Input and ideal output waveforms using a sine wave and square wave, respectively.  $R_1C_F = 1$  second and  $V_{oot} = 0$  V assumed.

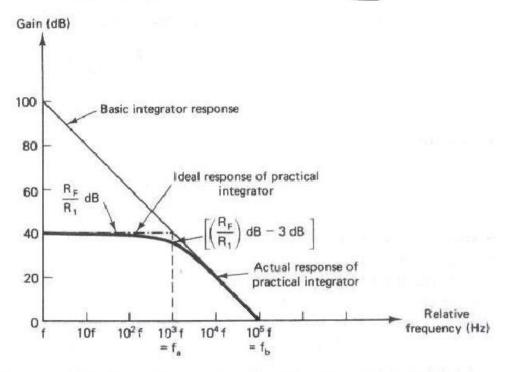

When  $v_{\rm in}=0$ , the integrator of Figure works as an open-loop amplifier. This is because the capacitor  $C_F$  acts as an open circuit  $(X_{CF}=\infty)$  to the input offset voltage  $V_{io}$ . In other words, the input offset voltage  $V_{io}$  and the part of the input current charging capacitor  $C_F$  produce the error voltage at the output of the integrator. Therefore, in the practical integrator shown in Figure , to reduce the error voltage at the output, a resistor  $R_F$  is connected across the feedback capacitor  $C_F$ . Thus,  $R_F$  limits the low-frequency gain and hence minimizes the variations in the output voltage.

The frequency response of the basic integrator is shown in Figure . In this figure,  $f_b$  is the frequency at which the gain is 0 dB and is given by

$$f_b = \frac{1}{2\pi R_1 C_F}$$

Both the stability and the low-frequency roll-off problems can be corrected by the addition of a resistor  $\overline{R}_F$  as shown in the practical integrator of Figure

The frequency response of the practical integrator is shown in Figure by a dashed line. In this figure, f is some relative operating frequency, and for frequencies f to  $f_a$  the gain  $R_F/R_1$  is constant. However, after  $f_a$  the gain decreases at a rate of 20 dB/decade. In other words, between  $f_a$  and  $f_b$  the circuit of Figure

acts as an integrator. The gain-limiting frequency

$$f_a$$

is given by

$$f_a = \frac{1}{2\pi R_F C_F}$$

Generally, the value of  $f_a$  and in turn  $R_1C_F$  and  $R_FC_F$  values should be selected such that  $f_a < f_b$ . For example, if  $f_a = f_b/10$ , then  $R_F = 10R_1$ .

Figure Frequency response of basic and practical integrators.  $f_a = 1/(2\pi R_F C_F)$  and  $f_b = 1/(2\pi R_1 C_F)$ .

Figure Practical integrator.

input signal will be integrated properly if the time period T of the signal is larger than or equal to  $R_FC_F$ . That is,

$$T \ge R_F C_F$$

where

$$R_F C_F = \frac{1}{2\pi f_a}$$

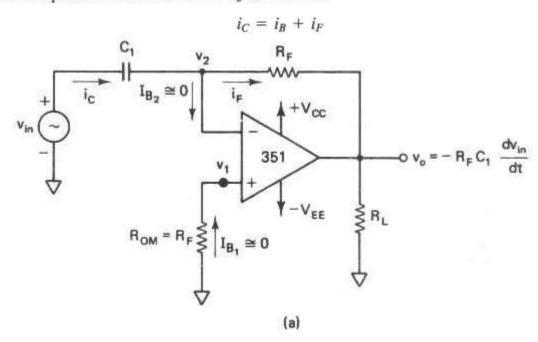

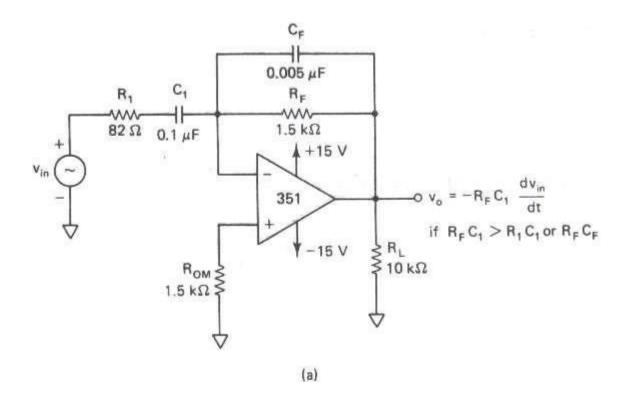

### THE DIFFERENTIATOR

Figure shows the differentiator or differentiation amplifier. As its name implies, the circuit performs the mathematical operation of differentiation; that is, the output waveform is the derivative of the input waveform. The differentiator may be constructed from a basic inverting amplifier if an input resistor  $R_1$  is replaced by a capacitor  $C_1$ .

The expression for the output voltage can be obtained from Kirchhoff's current equation written at node  $v_2$  as follows:

Since  $I_B \cong 0$ ,

$$i_C = i_F$$

$$C_1 \frac{d}{dt} (v_{\text{in}} - v_2) = \frac{v_2 - v_o}{R_F}$$

But  $v_1 = v_2 \cong 0$  V, because A is very large. Therefore,

$$C_1 \frac{dv_{\rm in}}{dt} = -\frac{v_o}{R_F}$$

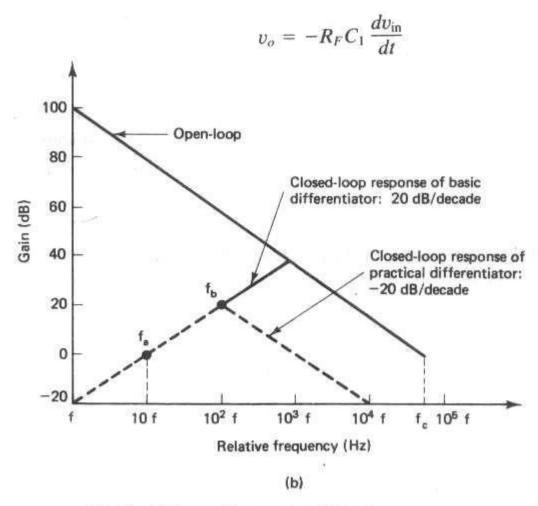

Figure Basic differentiator. (a) Circuit. (b) Frequency response.

The gain of the circuit  $(R_F/X_{C1})$  increases with increase in frequency at a rate of 20 dB/decade. This makes the circuit unstable. Also, the input impedance  $X_{C1}$  decreases with increase in frequency, which makes the circuit very susceptible to high-frequency noise. When amplified, this noise can completely override the differentiated output signal. The frequency response of the basic differentiator is shown in Figure .— In this figure,  $f_a$  is the frequency at which the gain is 0 dB and is given by

$$f_a = \frac{1}{2\pi R_F C_1}$$

Also,  $f_c$  is the unity gain-bandwidth of the op-amp, and f is some relative operating frequency.

Both the stability and the high-frequency noise problems can be corrected by the addition of two components:  $R_1$  and  $C_F$ , as shown in Figure This circuit is a practical differentiator, the frequency response of which is shown in Figure 7-27(b) by a dashed line. From frequency f to  $f_b$ , the gain increases at 20 dB/decade. However, after  $f_b$  the gain decreases at 20 dB/decade. This 40-dB/decade change in gain is caused by the  $R_1C_1$  and  $R_FC_F$  combinations. The gain-limiting frequency  $f_b$  is given by

$$f_b = \frac{1}{2\pi R_1 C_1}$$

where  $R_1 C_1 = R_F C_F$ .

turn  $R_1C_1$  and  $R_FC_F$  values should be selected such that

$$f_a < f_b < f_c$$

$$f_a = \frac{1}{2\pi R_F C_1}$$

$$f_b = \frac{1}{2\pi R_1 C_1} = \frac{1}{2\pi R_F C_F}$$

$$f_c = \text{unity gain-bandwidth}$$

The input signal will be differentiated properly if the time period T of the input signal is larger than or equal to  $R_FC_1$ . That is,

$$T \geq R_F C_1$$

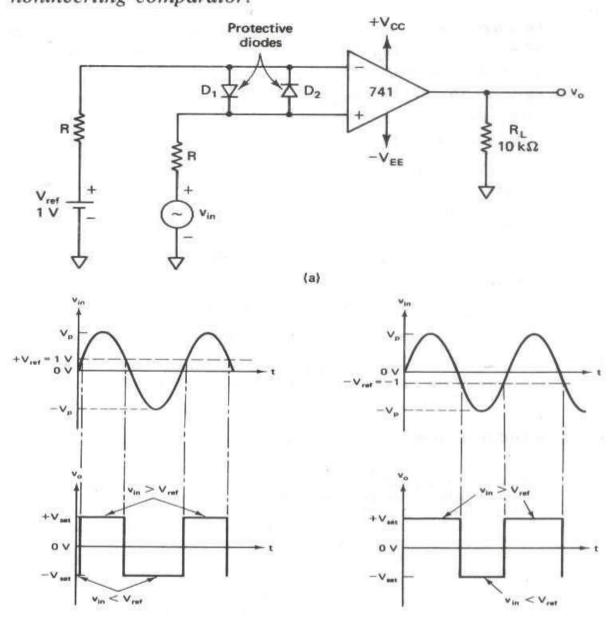

### BASIC COMPARATOR

Figure shows an op-amp used as a comparator. A fixed reference voltage  $V_{\text{ref}}$  of 1 V is applied to the (-) input, and the other time-varying signal voltage  $v_{\text{in}}$  is applied to the (+) input. Because of this arrangement, the circuit is called the noninverting comparator.

When  $v_{\rm in}$  is less than  $V_{\rm ref}$ , the output voltage  $v_o$  is at  $-V_{\rm sat}$  ( $\cong -V_{EE}$ ) because the voltage at the (-) input is higher than that at the (+) input. On the other hand, when  $v_{\rm in}$  is greater than  $V_{\rm ref}$ , the (+) input becomes positive with respect to the (-) input, and  $v_o$  goes to  $+V_{\rm sat}$  ( $\cong +V_{CC}$ ). Thus  $v_o$  changes from one saturation level to another whenever  $v_{\rm in} \cong V_{\rm ref}$ , as shown in Figure

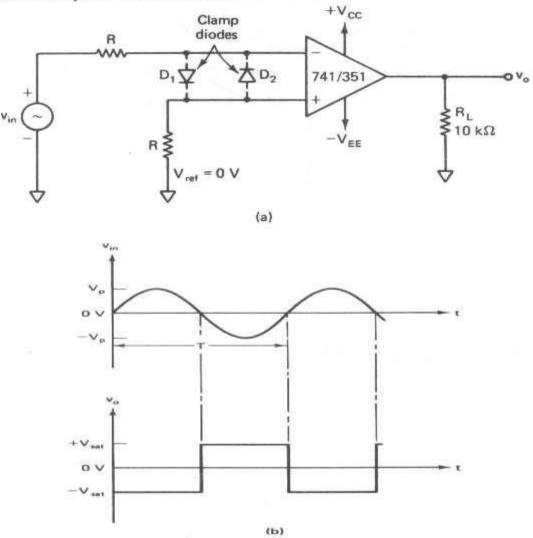

## ZERO-CROSSING DETECTOR

An immediate application of the comparator is the zero-crossing detector or sine wave-to-square wave converter.

Figure 9-3 (a) Zero-crossing detector. (b) Its typical input and output waveforms.

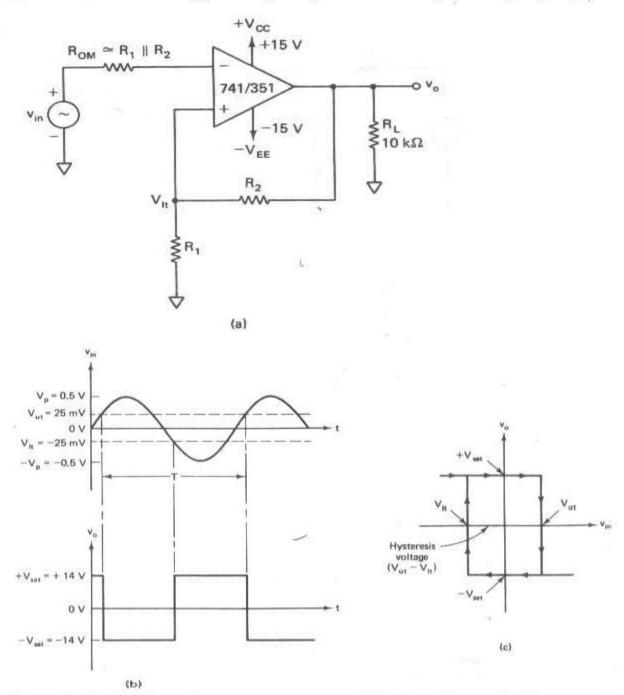

### SCHMITT TRIGGER

Figure shows an inverting comparator with positive feedback. This circuit converts an irregular-shaped waveform to a square wave or pulse. The circuit is known as the Schmitt trigger or squaring circuit. The input voltage  $v_{in}$  triggers

Figure 9-4 (a) Inverting comparator as Schmitt trigger. (b) Input and output waveforms of Schmitt trigger. (c)  $v_o$  versus  $v_{in}$  plot of the hysterisis voltage.

In Figure , these threshold voltages are obtained by using the voltage divider  $R_1$ - $R_2$ , where the voltage across  $R_1$  is fed back to the (+) input. The voltage across  $R_1$  is a variable reference threshold voltage that depends on the value and polarity of the output voltage  $v_o$ . When  $v_o = +V_{\rm sat}$ , the voltage across  $R_1$  is called the *upper threshold voltage*,  $V_{\rm ut}$ . The input voltage  $v_{\rm in}$  must be slightly more positive than  $V_{\rm ut}$  in order to cause the output  $v_o$  to switch from  $+V_{\rm sat}$  to  $-V_{\rm sat}$ . As long as  $v_{\rm in} < V_{\rm ut}$ ,  $v_o$  is at  $+V_{\rm sat}$ . Using the voltage-divider rule,

$$V_{\rm ut} = \frac{R_1}{R_1 + R_2} (+V_{\rm sat})$$

On the other hand, when  $v_o = -V_{\rm sat}$ , the voltage across  $R_1$  is referred to as lower threshold voltage,  $V_{\rm lt}$ .  $v_{\rm in}$  must be slightly more negative than  $V_{\rm lt}$  in order to cause  $v_o$  to switch from  $-V_{\rm sat}$  to  $+V_{\rm sat}$ . In other words, for  $v_{\rm in}$  values greater than  $V_{\rm lt}$ ,  $v_o$  is at  $-V_{\rm sat}$ .  $V_{\rm lt}$  is given by the following equation:

$$V_{\rm lt} = \frac{R_1}{R_1 + R_2} \left( -V_{\rm sat} \right)$$

Thus, if the threshold voltages  $V_{\rm ut}$  and  $V_{\rm h}$  are made larger than the input noise voltages, the positive feedback will eliminate the false output transitions. Also, the positive feedback, because of its regenerative action, will make  $v_o$  switch faster between  $+V_{\rm sat}$  and  $-V_{\rm sat}$ . In Figure resistance  $R_{OM}\cong R_1\|R_2$  is used to minimize the offset problems.

The comparator with positive feedback is said to exhibit *hysteresis*, a deadband condition. That is, when the input of the comparator exceeds  $V_{\rm ut}$ , its output switches from  $+V_{\rm sat}$  to  $-V_{\rm sat}$  and reverts back to its original state,  $+V_{\rm sat}$ , when the input goes below  $V_{\rm tt}$ . The hysteresis voltage is, of course, equal to the difference between  $V_{\rm ut}$  and  $V_{\rm lt}$ . Therefore,

$$V_{\text{hy}} = V_{\text{ut}} - V_{\text{lt}}$$

$$= \frac{R_1}{R_1 + R_2} \left[ + V_{\text{sat}} - (-V_{\text{at}}) \right]$$

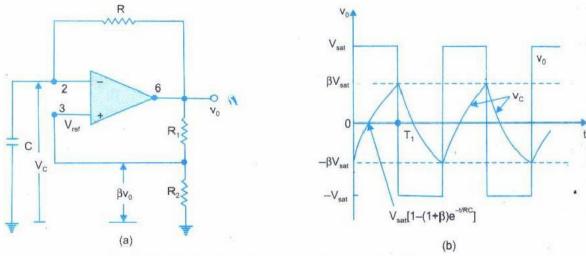

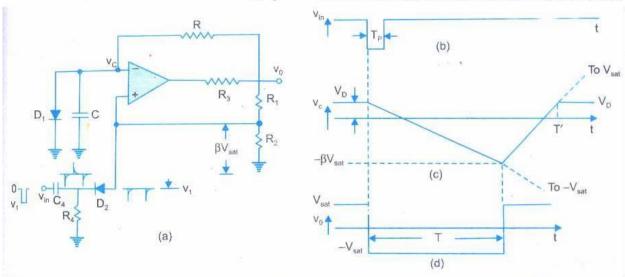

# SQUARE WAVE GENERATOR (ASTABLE MULTIVIBRATOR)

A simple op-amp square wave generator is shown in Fig. Also called a free running oscillator, the principle of generation of square wave output is to force an op-amp to operate in the saturation region. In Fig. fraction  $\beta = R_2/(R_1 + R_2)$  of the output is fed back to the (+) input terminal. Thus the reference voltage  $V_{\rm ref}$  is  $\beta v_{\rm o}$  and may take values as

Fig. 5.10 (a) Simple op-amp square wave generator (b) waveforms

$+\beta V_{\rm sat}$  or  $-\beta V_{\rm sat}$ . The output is also fed back to the (-) input terminal after integrating by means of a low-pass RC combination. Whenever input at the (-) input terminal just exceeds  $V_{\rm ref}$ , switching takes place resulting in a square wave output. In a stable multivibrator, both the states are quasi stable.

Consider an instant of time when the output is at  $+V_{\rm sat}$ . The capacitor now starts charging towards  $+V_{\rm sat}$  through resistance R, as shown in Fig. The voltage at the (+) input terminal is held at  $+\beta V_{\rm sat}$  by  $R_1$  and  $R_2$  combination. This condition continues as the charge on C rises, until it has just exceeded  $+\beta V_{\rm sat}$ , the reference voltage. When the voltage at the (-) input terminal becomes just greater than this reference voltage, the output is driven to  $-V_{\rm sat}$ . At this instant, the voltage on the capacitor is  $+\beta V_{\rm sat}$ . It begins to discharge through R, that is, charges toward  $-V_{\rm sat}$ . When the output voltage switches to  $-V_{\rm sat}$ , the capacitor charges more and more negatively until its voltage just exceeds  $-\beta V_{\rm sat}$ . The output switches back to  $+V_{\rm sat}$ . The cycle repeats itself as shown in Fig. 5.10 (b).

The frequency is determined by the time it takes the capacitor to charge from  $-\beta V_{\text{sat}}$  to  $+\beta V_{\text{sat}}$  and vice versa. The voltage across the capacitor as a function of time is given by,

$$v_{\rm c}(t) = V_{\rm f} + (V_{\rm i} - V_{\rm f})e^{-t/RC}$$

where, the final value,  $V_{\rm f} = + V_{\rm sat}$  and the initial value,  $V_{\rm i} = - \beta V_{\rm sat}$

Therefore,

$$\begin{aligned} v_{\rm c}(t) &= V_{\rm sat} + (-\beta V_{\rm sat} - V_{\rm sat}) \, e^{-t/RC} \\ v_{\rm c}(t) &= V_{\rm sat} - V_{\rm sat} \, (1+\beta) \, e^{-t/RC} \end{aligned}$$

or

At  $t = T_1$ , voltage across the capacitor reaches  $\beta V_{\rm sat}$  and switching takes place, Therefore,

$$v_c(T_1) = \beta V_{\text{sat}} = V_{\text{sat}} - V_{\text{sat}} (1 + \beta) e^{-T_1/RC}$$

After algebraic manipulation, we get,

$$T_1 = RC \ln \frac{1+\beta}{1-\beta}$$

This give only one half of the period.

Total time period

$$T = 2T_1 = 2RC \ln \frac{1+\beta}{1-\beta}$$

and the output wave form is symmetrical.

If  $R_1 = R_2$ , then  $\beta = 0.5$ , and  $T = 2RC \ln 3$ . And for  $R_1 = 1.16R_2$ , it can be seen that T = 2 RC

or

$$f_0 = \frac{1}{2RC}$$

The output swings from +  $V_{\rm sat}$  to -  $V_{\rm sat}$ , so,

$$v_{\rm o}$$

peak-to-peak = 2  $V_{\rm sat}$

# MONOSTABLE MULTIVIBRATOR

Monostable multivibrator has one stable state and the other is quasi stable state. The circuit is useful for generating single output pulse of adjustable time duration in response to a triggering signal. The width of the output pulse depends only on external components connected to the op-amp. The circuit shown in Fig.

is a modified form of the astable multivibrator.

Fig.

- (a) Monostable multivibrator (b) negative going triggering signal

- (c) capacitor waveform (d) output voltage waveform

A diode  $D_1$  clamps the capacitor voltage to 0.7V when the output is at  $+V_{\rm sat}$ . A negative going pulse signal of magnitude  $V_1$  passing through the differentiator  $R_4C_4$  and diode  $D_2$  produces a negative going triggering impulse and is applied to the (+) input terminal.

To analyse the circuit, let us assume that in the stable state, the output  $v_{\rm o}$  is at +  $V_{\rm sat}$ . The diode  $D_1$  conducts and  $v_{\rm c}$  the voltage across the capacitor C gets clamped to + 0.7V. The voltage at the (+) input terminal through  $R_1R_2$  potentiometric divider is +  $\beta V_{\rm sat}$ . Now, if a negative trigger of magnitude  $V_1$  is applied to the (+) input terminal so that the effective signal at this terminal is less than 0.7V i.e. ([ $\beta V_{\rm sat} + (-V_1)$ ] < 0.7 V), the output of the opamp will switch from +  $V_{\rm sat}$  to  $-V_{\rm sat}$ . The diode will now get reverse biased and the capacitor starts charging exponentially to  $-V_{\rm sat}$  through the resistance R. The voltage at the (+) input terminal is now  $-\beta V_{\rm sat}$ . When the capacitor voltage  $v_{\rm c}$  becomes just slightly more negative than  $-\beta V_{\rm sat}$ , the output of the op-amp switches back to +  $V_{\rm sat}$ . The capacitor C now starts charging to +  $V_{\rm sat}$  through R until  $v_{\rm c}$  is 0.7V as capacitor C gets clamped to the voltage. Various waveforms are shown in Fig. (b, c, d).

The pulse width T of monostable multivibrator is calculated as follows:

The general solution for a single time constant low pass RC circuit with  $V_i$  and  $V_f$  as initial and final values is,

$$v_0 = V_{\rm f} + (V_{\rm i} - V_{\rm f})e^{-t/RC}$$

For the circuit,  $V_{\rm f} = -V_{\rm sat}$  and  $V_{\rm i} = V_{\rm D}$  (diode forward voltage).

The output  $v_c$  is,

$$v_{\rm c} = -V_{\rm sat} + (V_{\rm D} + V_{\rm sat}) e^{-t/RC}$$

at t = T,

$$v_{\rm c} = -\beta V_{\rm sat}$$

Therefore,

$$-\beta V_{\text{sat}} = -V_{\text{sat}} + (V_{\text{D}} + V_{\text{sat}})e^{-T/RC}$$

After simplification, pulse width T is obtained as

$$T = RC \ln \frac{(1 + V_D/V_{\text{sat}})}{1 - \beta}$$

where

$$\beta = R_2/(R_1 + R_2)$$

If,

$$V_{\text{sat}} >> V_{\text{D}}$$

and  $R_1 = R_2$  so that  $\beta = 0.5$ , then

$$T = 0.69 \ RC$$

For monostable operation, the trigger pulse width  $T_p$  should be much less than T, the pulse width of the monostable multivibrator. The diode  $D_2$  is used to avoid malfunctioning by blocking the positive noise spikes that may be present at the differentiated trigger input.

# Unit-3

# **ACTIVE FILTERS AND TIMERS**

An electric filter is often a frequency-selective circuit that passes a specified band of frequencies and blocks or attenuates signals of frequencies outside this band. Filters may be classified in a number of ways:

- 1. Analog or digital

- 2. Passive or active

- 3. Audio (AF) or radio frequency (RF)

Analog filters are designed to process analog signals, while digital filters process analog signals using digital techniques. Depending on the type of elements used in their construction, filters may be classified as passive or active.

Elements used in passive filters are resistors, capacitors, and inductors. Active filters, on the other hand, employ transistors or op-amps in addition to the resistors and capacitors. The type of element used dictates the operating frequency range of the filter.

For example, RC filters are commonly used for audio\_or low- frequency operation, whereas LC or crystal filters are employed at RF\_or high –frequencies. Especially because of their high Q value (figure of merit), the crystal provide more stable operation at higher frequencies.

#### An active filter offers the following advantages over a passive filter:

- **1. Gain and frequency adjustment flexibility.** Since the op-amp is capable of providing a gain, the input signal is not attenuated as it is in a passive filter. In addition, the active filter is easier to tune or adjust.

- **2.** No loading problem. Because of the high input resistance and low output resistance of the opamp, the active filter does not cause loading of the source or load.

- **3.** Cost. Typically, active filters are more economical than passive filters. This is because of the variety of cheaper op-amps and the absence of inductors.

The most commonly used filters are these:

- 1. Low-pass filter

- 2. High-pass filter

- 3. Band-pass filter

- 4. Band-reject filter

- 5. All-pass filter

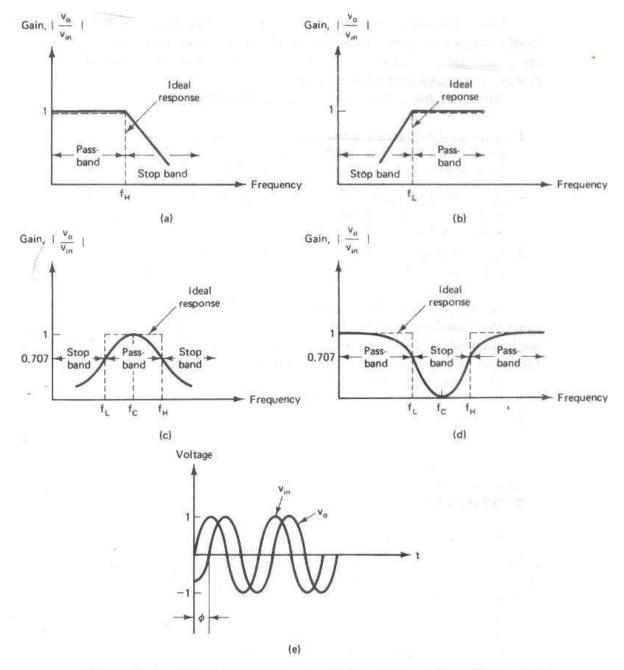

Figure 8-1 Frequency response of the major active filters. (a) Low pass. (b) High pass. (c) Band pass. (d) Band reject. (e) Phase shift between input and output voltages of an all-pass filter.

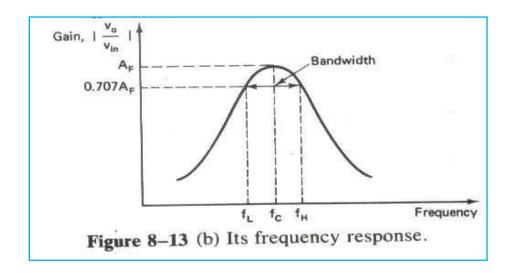

Fig. 8-1 shows the frequency response characteristics of the five types of filters. The ideal response is shown by dashed curves, while the solid lines indicate the practical filter response. A low-pass filter has a constant gain from 0 Hz to a high cutoff frequency f<sub>H</sub>. Therefore, the bandwidth is also f<sub>H</sub>.

At  $f_H$  the gain is down by 3 dB; after that  $(f > f_H)$  it decreases with the increase in input frequency. The frequencies between 0 Hz and  $f_H$  are known as the passband frequencies, whereas the range of frequencies, those beyond  $f_H$  that are attenuated includes the stopband frequencies.

Fig. 8-1(a) shows the frequency response of the low-pass filter. As indicated by the dashed line, an ideal filter has a zero loss in its passband and infinite loss in its stopband. Unfortunately, ideal filter response is not practical because linear networks cannot produce the discontinuities. However, it is possible to obtain a practical response that approximates the ideal response by using special design techniques, as well as precision component values and high-speed op-amps.

Butterworth, Chebyshev, and Cauer filters are some of the most commonly used practical filters that approximate the ideal response. The key characteristic of the Butterworth filter is that it has a flat passband as well as stopband. For this reason, it is sometimes called a flat-flat filter.

The Chebyshev filter has a ripple passband and flat stopband, i.e. the Cauer filter has a ripple passband and a ripple stopband. Generally, the Cauer filter gives the best stopband response among the three. Because of their simplicity of design, the low-pass and high-pass Butterworth filters are discussed here.

Figure 8-1(b) shows a high-pass filter with a stopband  $0 < f < f_L$  and a passband  $f > f_L$ .  $f_L$  is the low cutoff frequency, and f is the operating frequency. A band-pass filter has a passband between two cutoff frequencies  $f_H$  and  $f_L$ , where  $f_H > f_L$  and two stop-bands:  $0 < f < f_L$  and  $f > f_H$ . The bandwidth of the band-pass filter, therefore, is equal to  $f_H - f_L$ . The band-reject filter performs exactly opposite to the band-pass; that is, it has a band-stop between two cutoff frequencies  $f_H$  and  $f_L$  and two passbands:  $0 < f < f_L$  and  $f > f_H$ . The band-reject is also called a band-stop or band-elimination filter. The frequency responses of band- pass and band-reject filters are shown in Figure 8-1(c) and (d), respectively. In these figures,  $f_C$  is called the center frequency since it is approximately at the center of the passband or stopband.

Fig. 8.1(e) sows the phase shift between input and output voltages of an all-pass filter. This filter passes all frequencies equally well; that is, output and input voltages equal in amplitude for all frequencies, with the phase shift between the two a function of frequency. The highest frequency up to which the input and output amplitudes remain equal is dependent on the unity gain bandwidth of the op-amp. (At this frequency, however, the phase shift between the input and output is maximum.

The rate at which the gain of the filter changes in the stopband is determined by the order of the filter. For example, for the first order low-pass filter the gain-rolls-off at the rate of 20 dB/decade in the stopband, that is, for  $f>f_H$ ; on the other hand, for the second-order low-pass filter the roll-off rate is 40 dB/decade and so on. By contrast, for the first-order high-pass filter the gain increases at the rate of 20 dB/decade in the stopband, that is, until  $f=f_L$ ; the increase is  $40 \, \text{dB/decade}$  for the second-order high-pass filter;

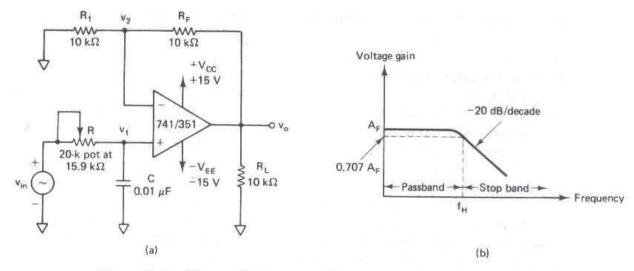

#### FIRST-ORDER LOW-PASS BUTTER WORTH FILTER

Fig. 8-2 shows a first-order low-pass Butterworth filter that uses an RC network for filtering. Note that the op-amp is used in the non-inverting configuration; hence it does not load down the RC network. Resistors R1 and RF determine the gain of the filter.

According to the voltage-divider rule, the voltage at the non-inverting terminal (across capacitor C) is

$$v_1 = \frac{-jX_C}{R - jX_C} v_{\text{in}}$$

$$j = \sqrt{-1} \quad \text{and} \quad -jX_C = \frac{1}{j2\pi fC}$$

$$v_1 = \frac{v_{\text{in}}}{1 + j2\pi fRC}$$

$$v_{\emptyset} = \left(1 + \frac{R_F}{R_1}\right) v_1$$

$$v_o = \left(1 + \frac{R_F}{R_1}\right) \frac{v_{\text{in}}}{1 + j2\pi fRC}$$

$$\frac{v_o}{v_{\text{in}}} = \frac{A_F}{1 + j(f/f_H)}$$

where  $\frac{v_o}{v_{\text{in}}}$  = gain of the filter as a function of frequency  $A_F = 1 + \frac{R_F}{R_1}$  = passband gain of the filter

$$f = \text{frequency of the input signal}$$

$$f_H = \frac{1}{2\pi RC} = \text{high cutoff frequency of the filter}$$

Figure 8-2 First-order low-pass Butterworth filter. (a) Circuit. (b) Frequency response.

The gain magnitude and phase angle equations of the low-pass filter can be obtained by converting Equation (1) into its equivalent polar form, as follows:

$$\left| \frac{v_o}{v_{in}} \right| = \frac{A_F}{\sqrt{1 + (f/f_H)^2}}$$

$$\phi = -\tan^{-1} \left( \frac{f}{f_H} \right)$$

Where  $\varphi$  is the phase angle in degrees.

The operation of the low-pass filter can be verified from the gain magnitude equation, (2):

1. At very low frequencies, that is,

$$f < f_H$$

,  $\left| \frac{v_o}{v_{\rm in}} \right| \cong A_F$

2. At

$$f = f_H$$

,  $\left| \frac{v_o}{v_{in}} \right| = \frac{A_F}{\sqrt{2}} = 0.707 A_F$

3. At

$$f > f_H$$

,  $\left| \frac{v_o}{v_{in}} \right| < A_F$

#### Filter Design

A low-pass filter can be designed by implementing the following steps:

- 1. Choose a value of high cutoff frequency  $f_H$ .

- 2. Select a value of C less than or equal to 1  $\mu$ F. Mylar or tantalum capacitors are recommended for better performance.

- 3. Calculate the value of R using

$$R = \frac{1}{2\pi f_H C}$$

4. Finally, select values of R1 and R<sub>F</sub> dependent on the desired passband gain A<sub>F</sub> using

$$A_F = 1 + \frac{R_F}{R_1}$$

#### **Frequency Scaling**

Once a filter designed; there may sometimes be a need to change its cutoff frequency. The procedure used to convert an original cutoff frequency  $f_H$  to a new cutoff frequency  $f_H$  is called frequency scaling. Frequency scaling is accomplished as follows. To change a high cutoff frequency, multiple R or C. but not both, by the ratio of the original cutoff frequency to the new cutoff frequency.

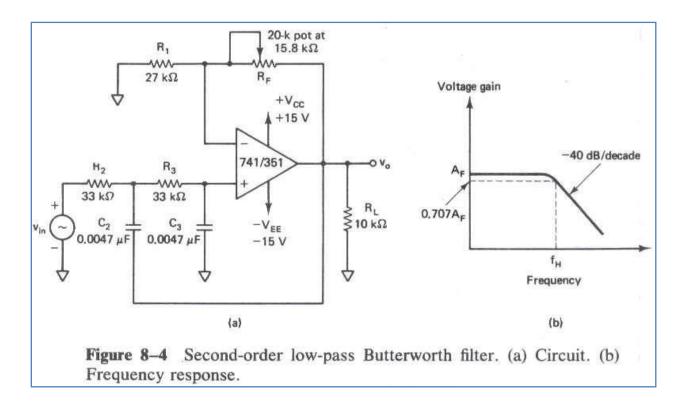

#### SECOND-ORDER LOW-PASS BUTTER WORTH FILTER

A stop-band response having a 40-dB/decade roll-off is obtained with the second order low-pass filter. A first-order low-pass filter can be converted into a second order type simply by using an additional RC network, as shown in Fig. 8-4.

Second-order filters are important because higher-order filters can be designed using them. The gain of the second-order filter is set by R1 and  $R_F$ , while the high cutoff frequency  $f_H$  is determined by R2, C2, R3, and C3, as follows:

$$f_H = \frac{1}{2\pi \sqrt{R_2 R_3 C_2 C_3}}$$

Furthermore, for a second-order low-pass Butterworth response, the voltage gain magnitude equation is

$$\left|\frac{v_o}{v_{\rm in}}\right| = \frac{A_F}{\sqrt{1 + (f/f_H)^4}}$$

where  $A_F = 1 + \frac{R_F}{R_1}$  = passband gain of the filter

$$f = \text{frequency of the input signal (Hz)}$$

$$f_H = \frac{1}{2\pi\sqrt{R_2R_3C_2C_3}} = \text{high cutoff frequency (Hz)}$$

#### FIRST-ORDER HIGH-PASS BUITERWORTH FILTER

High-pass filters are often formed simply by interchanging frequency-determining resistors and capacitors in low-pass filters. That is, a first-order high-pass filter is formed from a first-order low-pass type by interchanging components R and C.

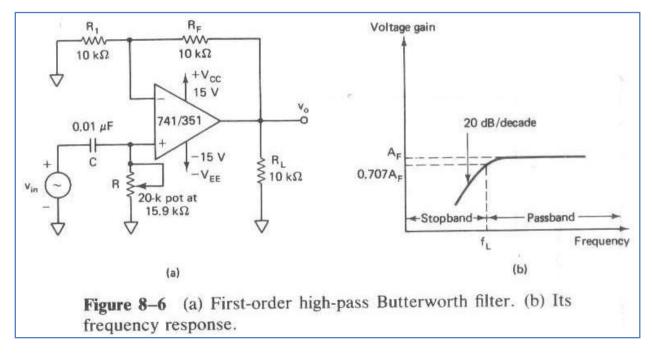

Similarly, a second-order high-pass filter is obtained from a second-order low-pass filter if R and C are interchanged, and so on. Figure 8-6 shows a first-order high- pass Butterworth filter with a low cutoff frequency of  $f_L$ .

This is the frequency at which the magnitude of the gain is 0.707 times its passband value. Obviously, all frequencies higher than  $f_L$  are passband frequencies, with the highest frequency determined by the closed-loop bandwidth of the op-amp.

Note that the high-pass filter of Figure 8-6(a) and the low-pass filter of Figure 8-2(a) are the same circuits, except that the frequency-determining components (R and C) are interchanged.

For the first-order high-pass filter of Figure 8-6(a), the output voltage is

$$v_o = \left(1 + \frac{R_F}{R_1}\right) \frac{j2\pi fRC}{1 + j2\pi fRC} v_{\rm in}$$

$$\frac{v_o}{v_{\rm in}} = A_F \left[ \frac{j(f/f_L)}{1 + j(f/f_L)} \right]$$

where

$$A_F = 1 + \frac{R_F}{R_1}$$

= passband gain of the filter  $f$  = frequency of the input signal (Hz)  $f_L = \frac{1}{2\pi RC}$  = low cutoff frequency (Hz)

Hence the magnitude of the voltage gain is

$$\left|\frac{v_o}{v_{\rm in}}\right| = \frac{A_F(f/f_L)}{\sqrt{1 + (f/f_L)^2}}$$

Since high-pass filters are formed from low-pass filters simply by interchanging R's and C's, the design and frequency scaling procedures of the low-pass filters are also applicable to the high- pass filters.

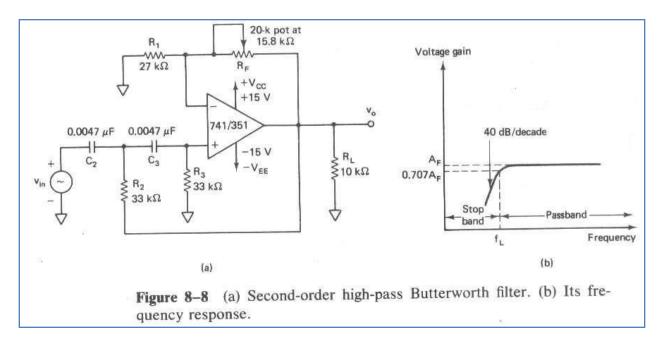

#### SECOND-ORDER HIGH-PASS BUTTERWORTH FILTER

As in the case of the first-order filter, a second-order high-pass filter can be formed from a second-order low-pass filter simply by interchanging the frequency-determining resistors and capacitors. Figure 8-8(a) shows the second-order high-pass filter.

The voltage gain magnitude equation of the second-order high-pass filter is as follows:

$$\left|\frac{v_o}{v_{\rm in}}\right| = \frac{A_F}{\sqrt{1 + (f_L/f)^4}}$$

Where  $A_F = 1.586 = passband gain for the second-order Butterworth response$

f = frequency of the input signal (Hz)

$f_L$  = low cutoff frequency (Hz)

Since second-order low-pass and high-pass filters are the same circuits except that the positions of resistors and capacitors are interchanged, the design and frequency scaling procedures for the high-pass filter are the same as those for the low-pass filter.

#### **BAND-PASS FILTERS**

A band-pass filter has a passband between two cutoff frequencies  $f_H$  and  $f_L$  such that  $f_H > f_L$ . Any input frequency outside this passband is attenuated.

Basically, there are two types of band-pass filters:

- (1) Wide band pass, and

- (2) Narrow band pass.

Unfortunately, there is no set dividing line between the two. However, we will define a filter as wide band pass if its figure of merit or quality factor Q<10.On the other hand, if we will call the filter a narrow band-pass filter. Thus Q is a measure of selectivity, meaning the higher the value Q, the more selective is the filter or the narrower its bandwidth (BW). The relationship between Q, the 3-dB bandwidth, and the center frequency fc is given by

$$Q = \frac{f_C}{\text{BW}} = \frac{f_C}{f_H - f_L}$$

For the wide band-pass filter the center frequency fc can be defined as

$$f_C = \sqrt{f_H f_L}$$

where  $f_H$  = high cutoff frequency (Hz)

$f_L$  = low cutoff frequency of the wide band-pass filter (Hz)

In a narrow band-pass filter, the output voltage peaks at the center frequency.

#### Wide band-pass filter

A wide band-pass filter can be formed by simply cascading high-pass and low-pass sections and is generally the choice for simplicity of design and performance.

To obtain  $\pm 20 dB/decade$  band-pass, first-order high pass and first order low-pass sections are cascaded; for a  $\pm 40 - dB/decade$  band-pass filter, second-order high- pass and second-order low-pass sections are connected in series.

The order of the band-pass filter depends on the order of the high- pass and low-pass filter sections.

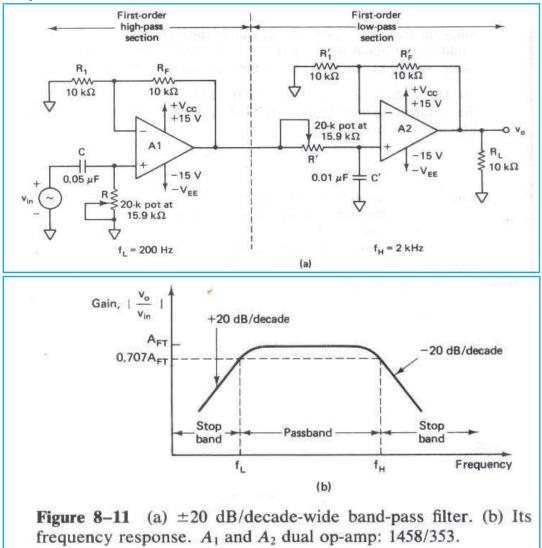

Figure 8-11 shows the  $\pm 20$ -dB/decade wide band-pass filter, which is composed of first-order high-pass and first-order low-pass filters. To realize a band- pass response, however,  $f_H$  must be larger than  $f_L$ .

Since the band-pass gain is 4, the gain of the high-pass as well as low-pass sections could be set equal to 2. That is, input and feedback resistors must be equal in value, say  $10 \text{ k}\Omega$  each. The complete band-pass filter is shown in Figure 8-11(a).

(b) The voltage gain magnitude of the band-pass filter is equal to the product of the voltage gain magnitudes of the high-pass and low-pass filters. Therefore, from Equations (8-2a) and (8-6),

$$\left| \frac{v_o}{v_{\text{in}}} \right| = \frac{A_F}{\sqrt{1 + (f/f_H)^2}} \qquad \left| \frac{v_o}{v_{\text{in}}} \right| = \frac{A_F(f/f_L)}{\sqrt{1 + (f/f_L)^2}}$$

$$\left| \frac{v_o}{v_{\text{in}}} \right| = \frac{A_{FT}(f/f_L)}{\sqrt{[1 + (f/f_L)^2][1 + (f/f_H)^2]}}$$

where  $A_{FT}$  = total passband gain

f = frequency of the input signal (Hz)

$f_L$  = low cutoff frequency (Hz)

$f_H$  = high cutoff frequency (Hz)

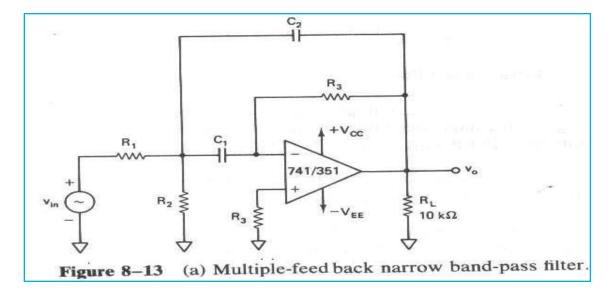

#### **Narrow Band-Pass Filter**

The narrow band-pass filter using multiple feedback is shown in Figure 8-13. As shown in this figure, the filter uses only one op-amp. Compared to all the filters discussed so far, this filter is unique in the following respects:

- 1. It has two feedback paths, hence the name multiple-feedback filter.

- 2. The op-amp is used in the inverting mode. :

Generally, the narrow band-pass filter is designed for specific values of center frequency fc and Q or fc and bandwidth. The circuit components are determined from the following relationships. To simplify the design calculations, choose C1 = C2 = C.

$$R_1 = \frac{Q}{2\pi f_C C A_F}$$

$R_2 = \frac{Q}{2\pi f_C C (2Q^2 - A_F)}$   $R_3 = \frac{Q}{\pi f_C C}$

Where  $A_F$  is the gain at fc, given by

$$A_F = \frac{R_3}{2R_1}$$

The gain  $A_F$ , however, must satisfy the condition

$$A_F < 20^2$$

Another advantage of the multiple feedback filter of Figure 8-13 is that its center frequency fc can be changed to a new frequency fc without changing the gain or bandwidth. This is accomplished simply by changing  $R_2$  to  $R_2$  so that

$$R_2' = R_2 \left(\frac{f_C}{f_C'}\right)^2$$

#### **BA ND-REJECT FILTERS**

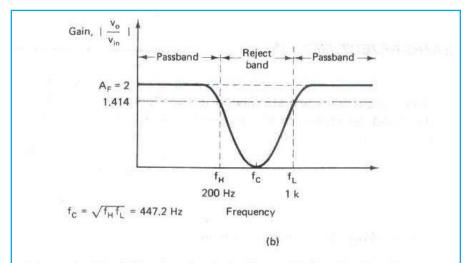

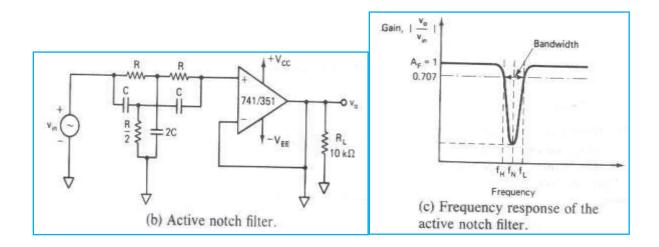

The band-reject filter is also called a band-stop or band-elimination filter. In this filter, frequencies are attenuated in the stopband while they are passed outside this band, as shown in Figure 8-1(d).

As with band-pass filters, the band-reject filters can also be classified as (1) wide band-reject or (2) narrow band-reject. The narrow band-reject filter is commonly called the notch filter. Because of its higher Q (>10), the bandwidth of the narrow band-reject filter is much smaller than that of the wide band-reject filter.

#### Wide Band-Reject Filter

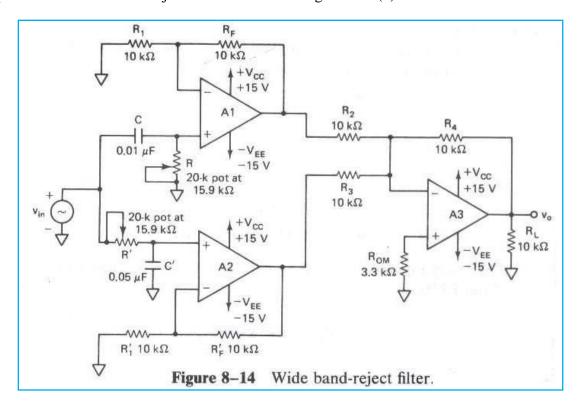

Figure 8-14(a) shows a wide band-reject filter using a low-pass filter, a high-pass filter, and a summing amplifier. To realize a band-reject response, the low cutoff frequency  $f_L$  of the high-pass filter must be larger than the high cutoff frequency  $f_H$  of the low-pass filter. In addition, the passband gain of both the high-pass and low-pass sections must be equal. The frequency response of the wide band-reject filter is shown in Figure 8-14(b).

**Figure 8–14** Wide band-reject filter. (a) Circuit. (b) Frequency response. For  $A_1$ ,  $A_2$ , and  $A_3$  use quad op-amp  $\mu$ AF774/MC34004.

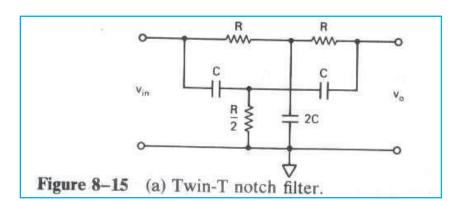

#### **Narrow Band-Reject Filter**

The narrow band-reject filter, often called the notch filter, is commonly used for the rejection of a single frequency such as the 60-Hz power line frequency hum. The most commonly used notch filter is the twin-T network shown in Figure 8-15(a). This is a passive filter composed of two T-shaped networks. One T network is made up of two resistors and a capacitor, while the other uses two capacitors and a resistor. The notch-out frequency is the frequency at which maximum attenuation occurs; it is given by

$$f_N = \frac{1}{2\pi RC}$$

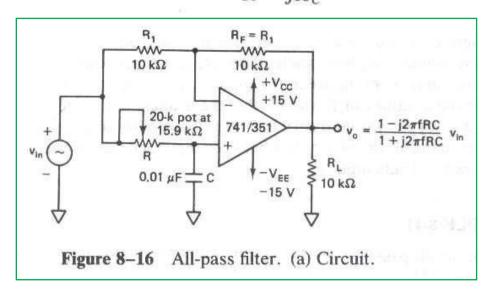

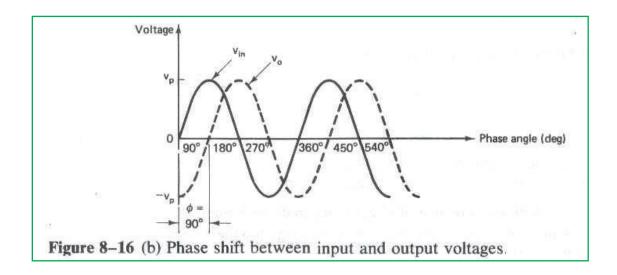

#### **ALL-PASS FILTER**

As the name suggests, an all-pass filter passes all frequency components of the input signal without attenuation, while providing predictable phase shifts for different frequencies of the input signal. When signals are transmitted over transmission lines, such as telephone wires, they undergo change in phase. To compensate for these phase changes, all-pass filters are required. The all-pass filters are also called delay equalizers or phase correctors. Figure 8-16(a) shows an all- pass filter wherein  $R_F = R_1$ . The output voltage Vo of the filter can be obtained by using the superposition theorem:

$$v_o = -v_{\rm in} + \frac{-jX_C}{R - jX_C} v_{\rm in}(2)$$

But -j = 1/j and  $X_C = 1/2 \prod fC$ . Therefore, substituting for  $X_C$  and simplifying, we get

$$v_o = v_{\rm in} \left( -1 + \frac{2}{j2\pi fRC + 1} \right)$$

$$\frac{v_o}{v_{\rm in}} = \frac{1 - j2\pi fRC}{1 + j2\pi fRC}$$

Where f is the frequency of the input signal in hertz.

Equation indicates that the amplitude of Vo/Vin is unity; that is, |Vo|=|Vin| throughout the useful frequency range, and the phase shift between Vo and Vin is a function of input frequency f. The phase angle  $\varphi$  is given by

$$\phi = -2 \tan^{-1} \left( \frac{2\pi fRC}{1} \right).$$

Where  $\varphi$  is in degrees, in hertz, R in ohms, and C in farads. Equation is used to find the phase angle  $\varphi$  if f, R, and C are known. Figure 8-16(b) shows a phase shift of 90° between the input Vin and output Vo. That is, Vo lags Vin by 90°. For fixed values of R and C, the phase angle  $\varphi$  changes from 0 to 180°as the frequency f is varied from 0 to  $\infty$ . In Figure 8-16(a), if the positions of R and C are interchanged, the phase shift between input and output becomes positive. That is, output Vo leads input Vin.

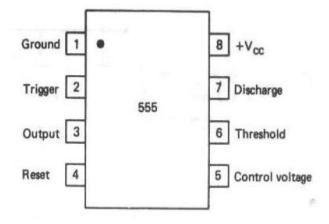

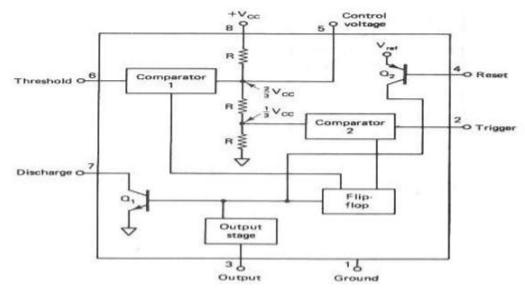

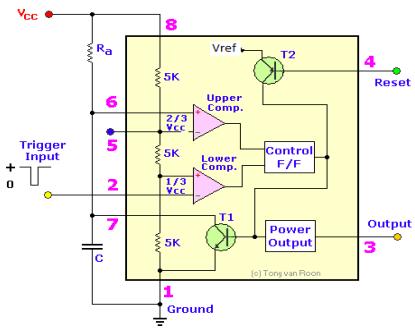

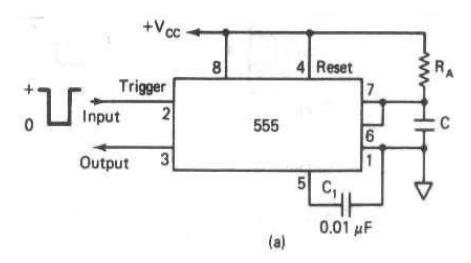

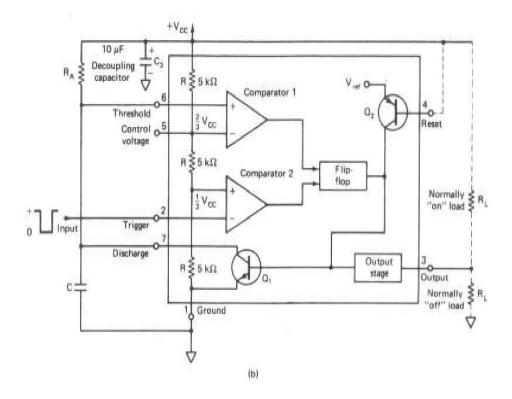

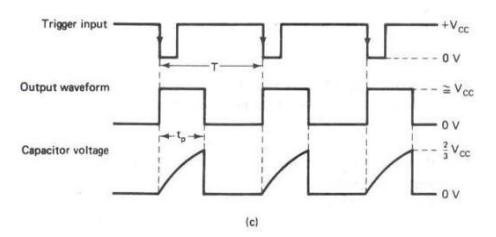

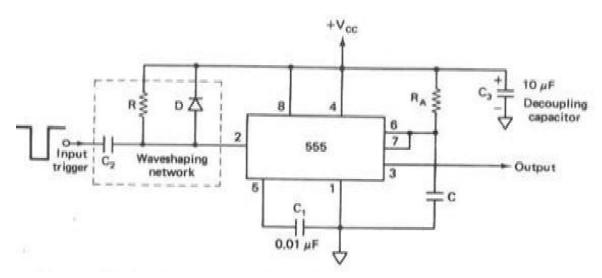

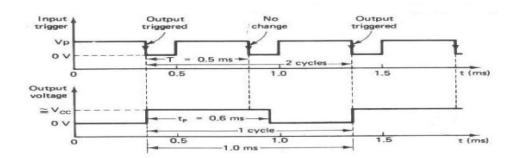

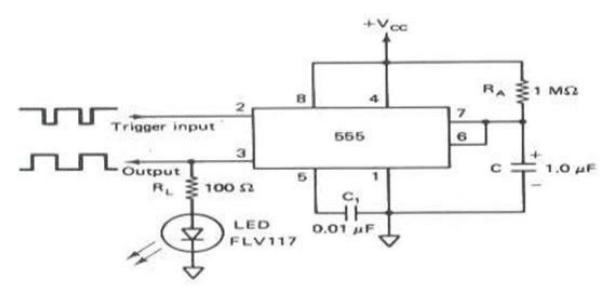

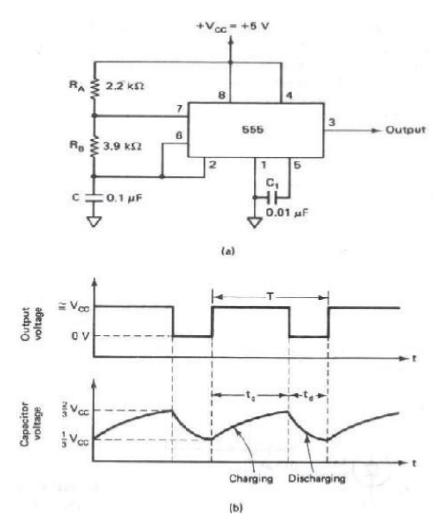

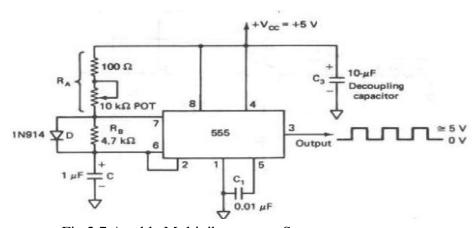

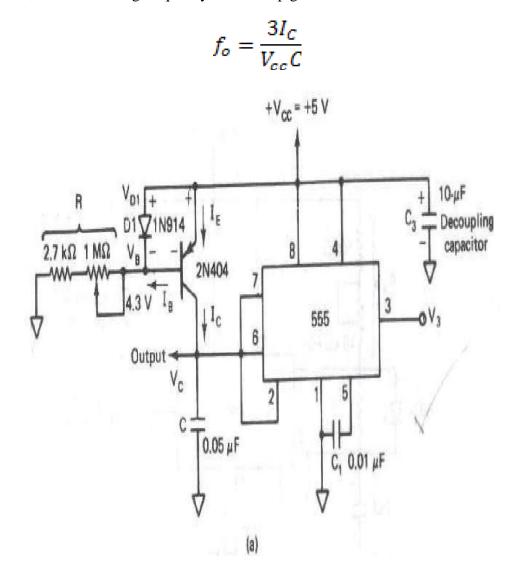

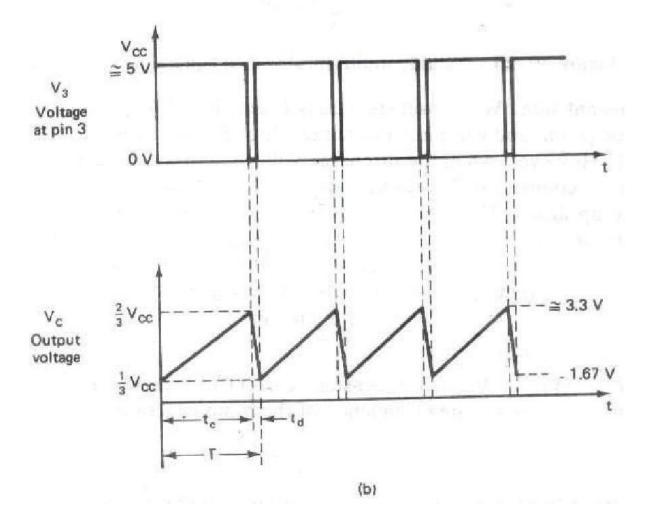

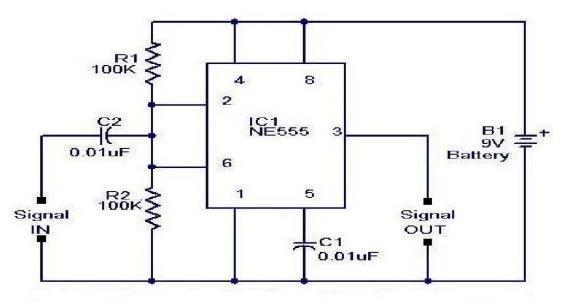

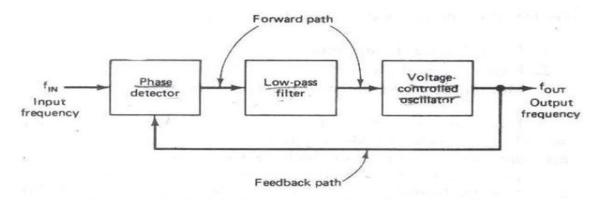

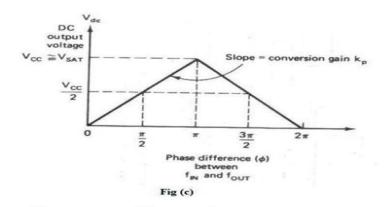

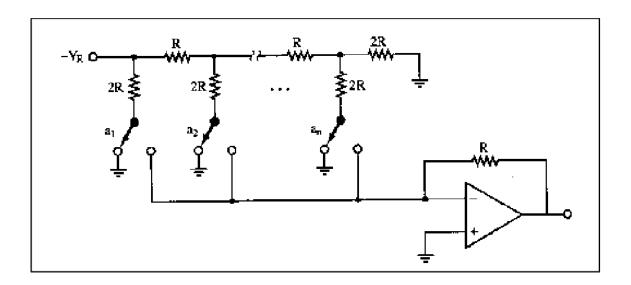

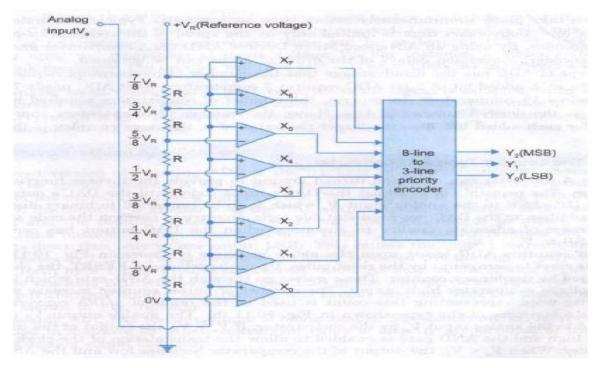

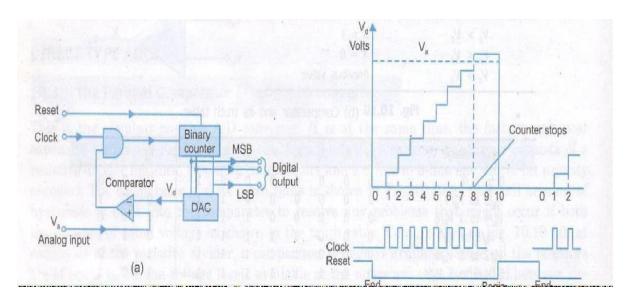

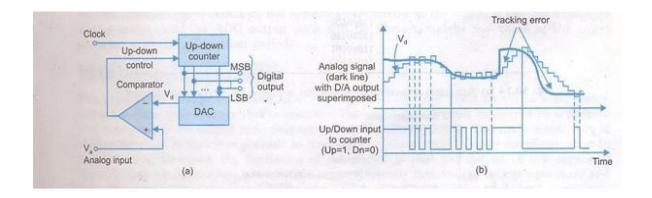

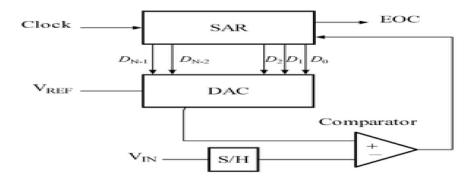

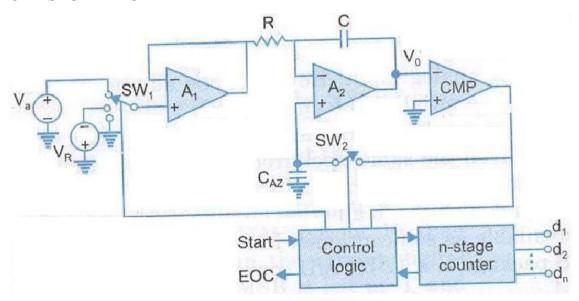

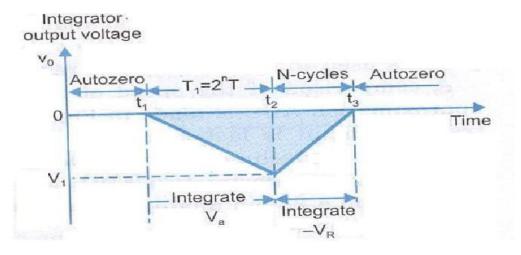

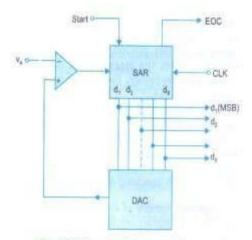

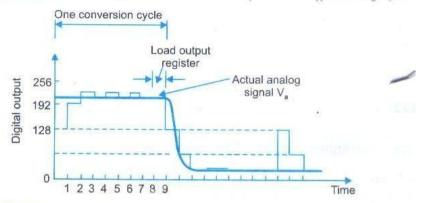

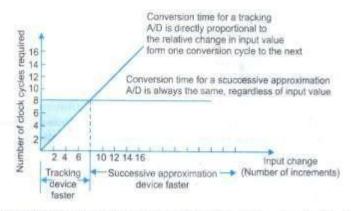

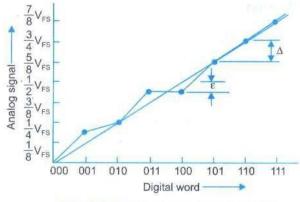

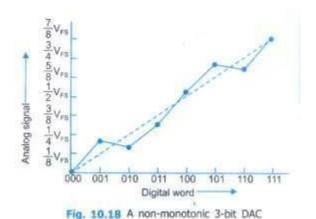

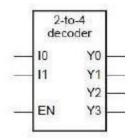

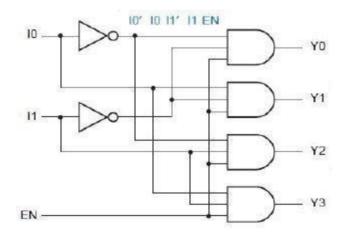

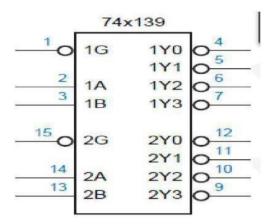

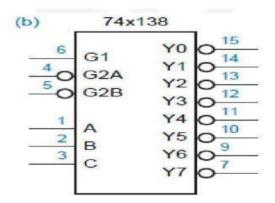

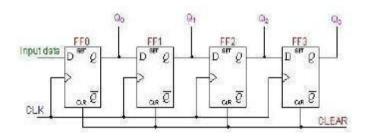

#### **INTRODUCTION TO 555 TIMER:**